pll带宽的选择具体依据是怎样的?

时间:10-02

整理:3721RD

点击:

(1)环振VCO的pll带宽越大越能抑制VCO的噪声,带宽越小越能抑制CP+PFD和Divider的噪声,所以说带宽选择要适中,但是具体的选择依据是怎样的?

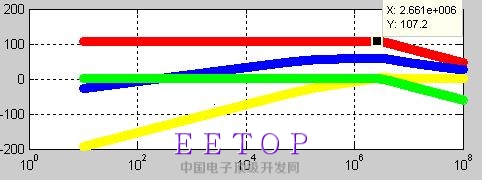

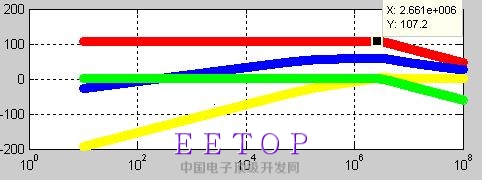

(2)如果只看噪声的传递函数,各个模块的传函波形打出来到一个图中,什么样的波形是我的目标呢?现在我仿真出来的是低频部分CP+PFD整体的闭环传函值最大,而且大很多,在带宽频点之后,随着低通和带通模块噪声的减小,高通的VCO噪声逐渐占主要部分。从数学表达式来看,这个趋势是不可改变的,那么我调整环路滤波器的电阻和电容以及Icp等参数想达到什么样的目标呢?

(3)又,如果选择了带宽w,那么w附近带外的频率对应的噪声大小要考虑吗?

(4)以上是只看噪声闭环传函的情况,看闭环传函也是有意义的吧,我了解到的还有仿真VCO等模块噪声,导出数据然后与其闭环传函相乘,这个是要准确一些,一定要这样做才有意义吗?

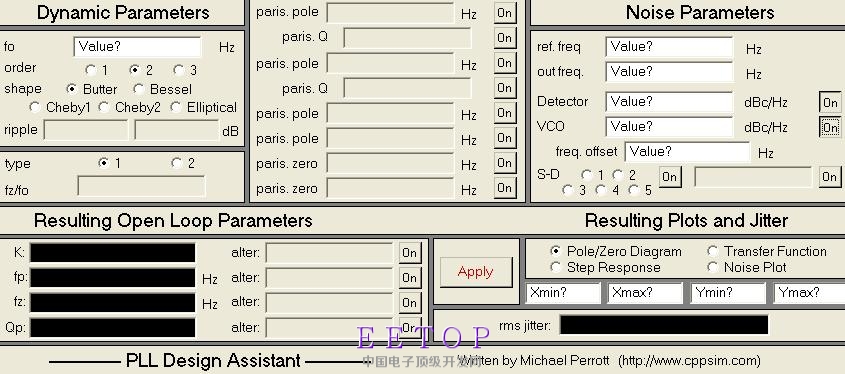

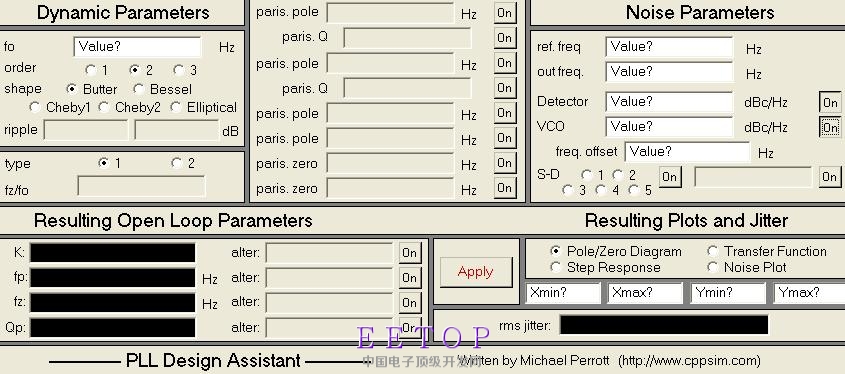

(5)CPPSIM软件中要填detector的噪声,这个怎么仿真得到呢?另外分频器和CP,低通滤波器的噪声都没有填的地方,这些不需要考虑?

问题有点儿多,求大神指点!上面的图是CPPSIM的界面,下面的图是各个模块的闭环传函。欢迎沟通讨论!

(2)如果只看噪声的传递函数,各个模块的传函波形打出来到一个图中,什么样的波形是我的目标呢?现在我仿真出来的是低频部分CP+PFD整体的闭环传函值最大,而且大很多,在带宽频点之后,随着低通和带通模块噪声的减小,高通的VCO噪声逐渐占主要部分。从数学表达式来看,这个趋势是不可改变的,那么我调整环路滤波器的电阻和电容以及Icp等参数想达到什么样的目标呢?

(3)又,如果选择了带宽w,那么w附近带外的频率对应的噪声大小要考虑吗?

(4)以上是只看噪声闭环传函的情况,看闭环传函也是有意义的吧,我了解到的还有仿真VCO等模块噪声,导出数据然后与其闭环传函相乘,这个是要准确一些,一定要这样做才有意义吗?

(5)CPPSIM软件中要填detector的噪声,这个怎么仿真得到呢?另外分频器和CP,低通滤波器的噪声都没有填的地方,这些不需要考虑?

问题有点儿多,求大神指点!上面的图是CPPSIM的界面,下面的图是各个模块的闭环传函。欢迎沟通讨论!

看输出的总噪声。看看博士论文吧。

最终带宽是根据相位噪声最优决定的。

ADPLL 可以实现,锁频阶段,只有P调节,大带宽,快速锁定频率。

到了锁相阶段,启动PI 调节,同时压低带宽,得到最优相位噪声。

可以各个模块行为级建模,然后,仿真来确定带宽。

噪声和稳定性 考虑啊,给其中一个范围,另一个做到最好。

博士论文我看了,确实像您说的,看的是各个模块的总噪声乘以对应的闭环传函,然后相加,得到总噪声,但是这个噪声波形是什么

样的才是我们想要的呢?如果选择了带宽w,那么w附近带外的频率对应的噪声大小要考虑吗?

相位噪声最优具体是哪个模块还是?怎么叫做最优?