温故而知新之二阶系统(补遗)

该系列前3期内容地址如下,该兴趣的可以回顾~

温故而知新之二阶系统(上) http://bbs.eetop.cn/thread-625164-1-1.html

温故而知新之二阶系统(中) http://bbs.eetop.cn/thread-626580-1-1.html

温故而知新之二阶系统(下) http://bbs.eetop.cn/thread-627896-1-1.html

这期内容会稍多一些,我们先来划重点。围绕以下几个问题,我们逐条分析回答。

1、次极点和GBW相对位置对相位裕度的影响?

2、固定GBW,次极点位置对阶跃响应速度的影响?

3、举个小例子吧。

对于第一个问题,

我们先思考一下单极点构成的闭环系统,如图1所示。这里增益带宽积GBW=y0ω1st,(后续如无特殊说明,GBW为rad/s的形式,注意Hz表示时的2Pi转换关系)。根据增益带宽积恒定的结论,当反馈系数为β时,有低频闭环增益约为1/β,闭环带宽约为βGBW,穿越频率也约为βGBW。这里不考虑反馈系数的频率特性,认为随频率变化恒定。

图1

图1所示的单极点闭环系统,由于环路增益(Loop Gain)仅包含一个极点,所以相位裕度为90度。

如果放大器是两个极点的形式(主极点ω1st和次极点ω2nd)。其闭环响应的形式和阻尼因子、无阻尼振荡频率关系如图2所示。有直观理解,如果存在次极点在穿越频率处,相移应该为-135度,相位裕度近似为45度。是需要稳定性考虑的情况。

图2中定义了次极点ω2nd和GBW的位置比例关系k,则无阻尼振荡频率,阻尼系数都可以表示为含有GBW、k和β的表达式。

图2

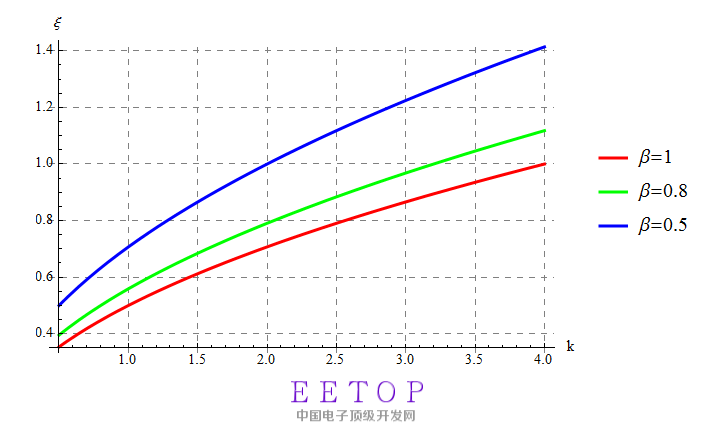

图3给出几种不同反馈系数β及次极点不同位置关系k时,阻尼因子的变化情况。其中k/β=4时,有ξ=1,是临界阻尼情况。时域响无过冲。当k/β=2β时,阻尼因子ξ=0.707,频域响应无尖峰。

图3

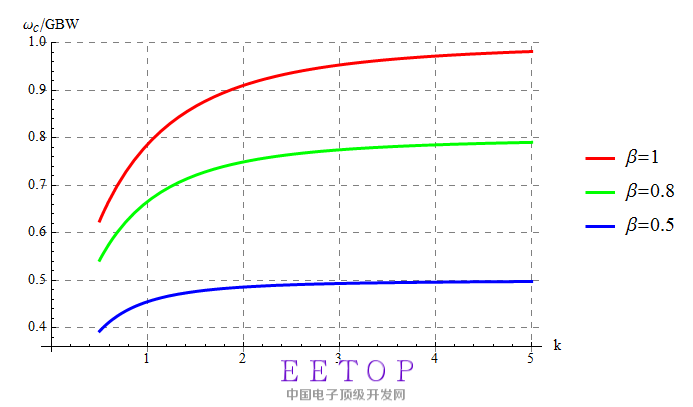

同样对于不同的反馈因子β和次极点位置比例k,可以得到穿越频率

ωc

和对应的相位裕度Φm与k/β关系的表达式,如图4所示。

图4

对于穿越频率表达式,绘制几种情况如图5所示。当次极点远离GBW时,也即k值较大,穿越频率即为闭环带宽βGBW(相当于单极点系统中,闭环增益为1/β的-3dB带宽)。当次极点越接近βGBW时,会比较明显的影响到穿越频率的实际位置。也即较低频率的次极点的存在使得穿越频率提前(小于βGBW)。

图5

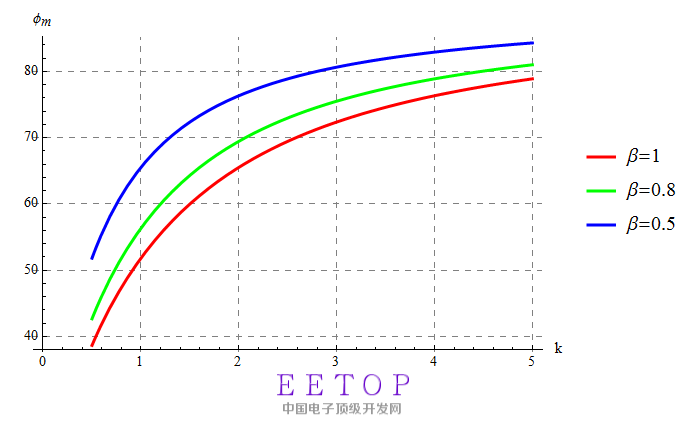

这里同样绘制得到相位裕度Φm,如图6。当次极点越靠近GBW时,相位裕度也越来越小。其中β=1时,次极点位于GBW处(k=1),有相位裕度约为52度。这是由于次极点的存在导致穿越频率比GBW小,注意这比直觉的45度相位裕度要大一些。原因也是因为次极点的存在使穿越频率提前(更低)。

这也要求我们在实际设计Opamp或OTA时,要注意控制次极点的位置。从而留足够大的相位裕度,保证时域有比较好的瞬态响应。

图6

所以,这里也就可以回答第一个问题了,对于固定的GBW,把次极点位置推离GBW频率处,可提升相位裕度。当次极点位置超过2βGBW时,阻尼因子大于0.707,频域闭环响应无尖峰。当次极点位置超过4βGBW时,阻尼因子大于1,时域响应无过冲。

对于第二个问题,时域响应到底和什么有关呢?容我慢慢解开其面纱。

这里我们还是先回顾图1所示的单极点闭环系统。可以看到,如果放大器只有一个主极点ω1st,有闭环带宽约为βGBW,也等于其时域阶跃响应的时间常数1/τ。

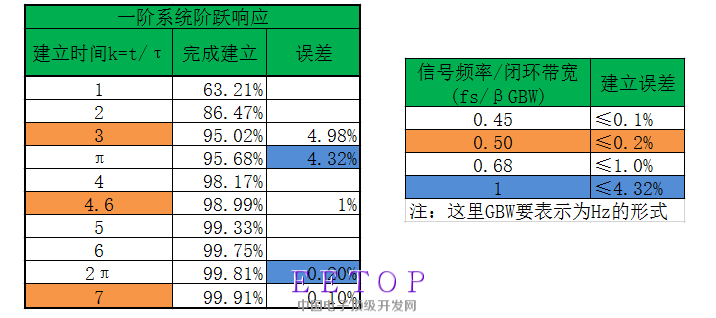

我们知道,对于一阶系统阶跃响应有如下的几个关系。4.6t和7t是个高精度的建立标准。注意,图7右的信号为占空比50%的方波。可以看到,如果信号频率为闭环带宽的一半时,可以达到0.2%的精度。

图7

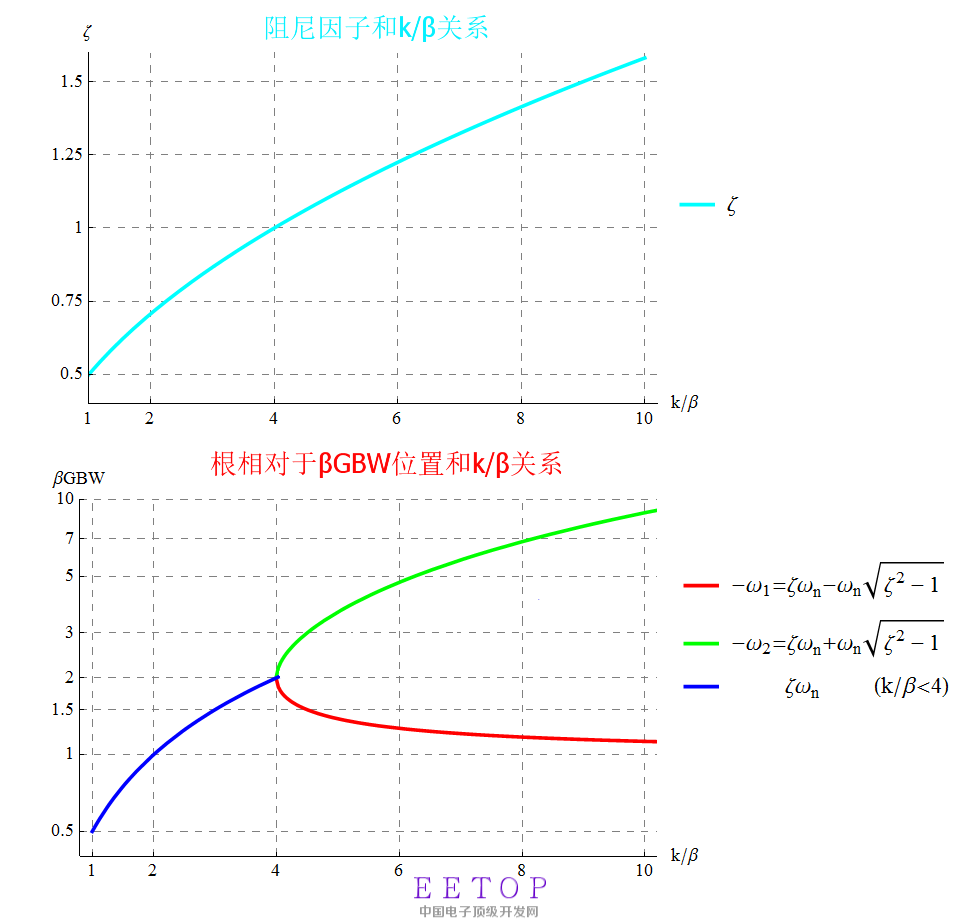

回忆先前的假设,GBW保持不变,关注次极点ω2nd和GBW的位置比例关系k。图8上,我们重新给出了阻尼系数和k/β的关系。其中k/β=4是临界阻尼。图8下,给出了k/β>4

时,两个实根(ω1闭环主极点,ω2闭环次极点)的轨迹。其中当k较大时,闭环主极点ω1趋向于-βGBW,也就是次极点频率较高时,可以看做闭环带宽为βGBW的单极点系统。

图8

也可以看到,当次极点接近4

βGBW,闭环主极点和次极点开始相互靠拢接近,并收敛到二重实根2

βGBW,达到了峰值。之后随着k/β进一步减小,闭环系统进入欠阻尼状态,其根实部如蓝色所示。这些表现在时域会是个什么效果那?

重写阶跃响应的近似表达式,如图9所示。其中参数为k/β,时间单位为βGBWt。

图9

绘制阶跃响应如图10(a)所示,这里固定βGBW,得到不同次极点位置及反馈系数情况下,和比值k/β的关系。建立接近完成的细节如图(b),可以看到k/β=4,也就是绿色线,是临界阻尼的情况,也是无过冲情况下最快的建立。当k/β<4时,欠阻尼下,存在时域过冲,不过建立会更快一些(更早到达稳态值)。具体还是要看应用场景吧,允不允许过冲存在。

图10

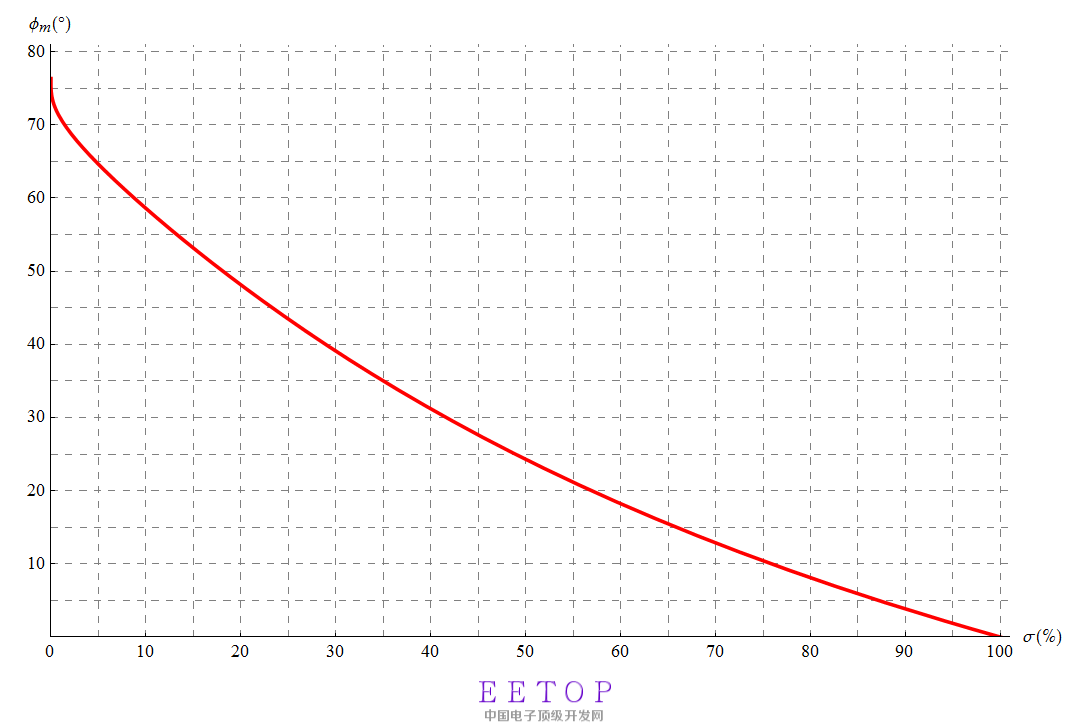

这里补充一个时域过冲的超调量σ和频域相位裕度Φm的对照关系,如图11。大多数时候还是会通过时域过冲的超调比例来进一步验证相位裕度是否充足。有几个特殊点,如阻尼因子ξ=0.707时,相位裕度为65.5°,超调量为4.3%。更多数据可以查看封面的结果。

图11

最后举个例子吧,对于单级驱动容性负载的OTA,可以认为主极点就在输出端,如图12(a)。这里为方便,反馈系数β=1,Buffer连接形式。一个典型的应用场景就是通过Buffer测试芯片内部的方波(或其他变化)信号,负载为空载或示波器探头的容性负载。为了减小Buffer引入的误差,对该OTA的要求包含了低频增益Dc Gain和增益带宽积GBW,设计时可以根据允许的误差范围和输入信号频率,合理分配静态和动态误差的贡献比例。

图12

更改一下结构,如图12(b)。OTA1保持不变,在OTA1和负载电容CL中间插入Buffer连接的OTA2。那么如果图(a)和图(b)输入信号一样,该如何设计OTA2及电容Cc。

这里OTA1、OTA2、Cc和CL构成了二阶放大器,系统总的为Buffer连接。为了保证空载时(CL=0)的稳定性,图12(b)中Cc处形成的极点通常作为主极点。那么OTA2的输出端电容Cc

的极点就是次极点了。

电容Cc:

为保证图12(b)能和图12(a)能够Buffer相同速度的输入信号。电容Cc应该小于等于CL。这样能够保证整个环路的GBW1大于等于图12(a)中的。

OTA2考虑:

OTA2的Buffer连接,从频域可以看做为单位增益,主极点为OTA2的增益带宽积GBW2的低通单极点子系统。这里就要考虑重载(CL=示波器探头的容性负载)时,OTA2的GBW2

和系统闭环带宽GBW1(βGBW=GBW1)的位置关系。比如满足GBW2>=4GBW1

,保证时域无过冲。或者激进一些满足GBW2>=2GBW1

,保证较快的响应速度,及OTA2较低的功耗。

注意OTA2按照重载设计。空载时,次极点位置在更高频率处,可以有更大的相位裕度。

好了,本期的内容就这么多了,二阶系统我们也算把相关内容都汇总在一起了,希望通过对基础理论的温习,进一步思考,指导我们的模拟电路设计。下期见吧。

也欢迎扫码关注小牛牛的公众号,可查看更多往期内容,也会第一时间看到最新更新~

感谢小编无私奉献,让我对二阶系统有了一个系统的、全新的理解。

感谢分享!

小编留溜达