cadence中怎么对adc测试INL与DNL?

1.怎么保存adc的输出结果?在spectre里能直接保存么?什么格式文件?

2.怎么把保存的文件导出来?毕竟在服务器上。

3.MATLAB是在本地仿真是么?MATLAB上还需要编写代码么?

4有没有相对简单的方法?有没有相关资料可以参考?

希望大神能不吝赐教!万分感谢!

在某论文的静态参数测试中看到这样一句话

用verilog—a编写的模块是什么模块?存储器?

看了何乐年的书之后,我可以把十位输出中的一位输出为一个文件了,可以通过matlab,把电压值转为1.0.

有大神么?

这个问题我可以帮你解决

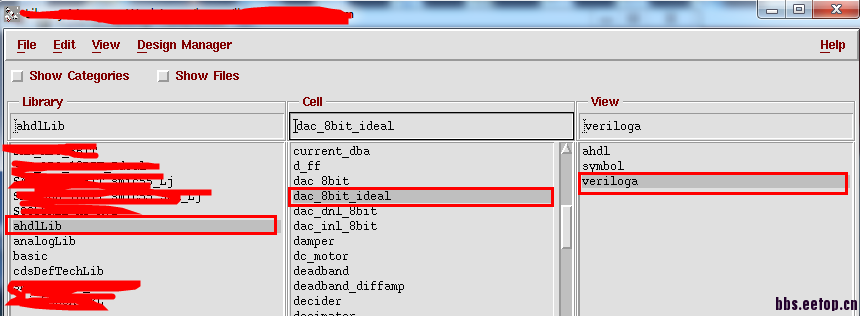

首先,利用cadence中理想的8位DAC改写成10位的DAC

即将数字码转换为模拟台阶。

跑够足够长的周期,相干采样,选取足够多的采样点,10位最少1024,如果需要测试INL和DNL,可以参考美信的Maltab代码,建议样本4096个点以上

谢谢你的回答,但是我是新手,有些还是不懂

cadence的理想DAC在哪里?analogLib中么?我找了好像没有

相干采样通过什么采样呢?ocean命令么?

美信matlab代码好找么?我先搜索下,你要是有能copy一份么?

还是说直接将波形导出,在matlab里面采样?

理想DAC是在verilog—a里面是吧?但是现在有个问题是打不开modelwriter了。之前点了不提示使用modelwriter,直接 text editer了

理想DAC在analoglib上面的alihld里面,是用Verilog-a写的理想模块,你可以将这个理想模块复制到自己的lib里面。然后通过改写里面的代码,将8位变为10位,改写不难,记得里面有vref和vtran,vref是你的参考电平,vtran是转换中间点。相干采样建议你自个看看书,这个不能拿一句我是新手就能敷衍过去。输入正弦波,正弦波的频率比上你ADC的采样频率=采样周期各数N比上采样个数M,这个M最小1024,建议4096.

美信的代码本区就有,你自己找找

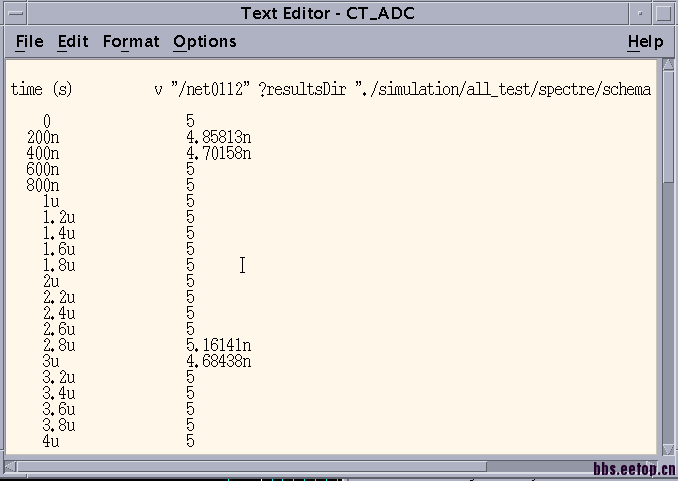

你10位的数字码输出后,经过理想DAC后会还原成模拟台阶。你在cadence波形里找到tool里面的table。里面我记得有些东西要填写,就是你选点的起始时间和截止时间,然后下面是你选择的采点间隔。这个不知道你ADC的具体参数,我就不跟你说具体数值了吧。填写完后点击Ok,就会出来波形采样点了,你选取1024(2048、4096)个采样点在matlab里跑fft,可以知道SNDR、SFDR、ENOB、THD等

INL和DNL也有相应的代码,你自己找找。

我想我应该表达得很清楚了,打字真累

在analoglib中没有找到你说的alihld这个模块呢。恩我现在大概懂这个流程了。就是用理想DAC转换成模拟波,再把波形导出。matlab的代码也找到了。现在问题是找不到理想DAC模块。在论坛里找了找,有说在verilog-a里的modelwriter里有理想模块的。但是我这cadence中打开verilog-a也不弹出modelwriter的窗口。所以现在是卡在第一步了。

大神,辛苦,辛苦。么么哒。已经很详细了。

不是在那个里面,是和它平行的里面,自己多找找,我估计拼写错误了。

我不是大大,我也是菜鸟,只是你做的跟我差不多

[img][/img]

辛苦了,截了个图。很明白10位的理想DAC已经搞出来了。根据帖子里前辈的代码,还有modelwriter里的综合起来写的。(话说verilog零基础啊,出波形的时候自己都感动的要哭了)

现在有个问题是,要相干采样,就是fin/fs=采样周期/采样数。问题又来了

1.做的采样频率在350khz,采样数听另一个前辈说最小1024,打算先用1024试试。那采样周期要与1024互质,就取了11周期,可以么?此时输入正弦信号为3.8364.周期数这样取值可以么?

2.仿真速度那叫一个慢啊。要获得1024个点,总共需要2.867ms。我仿了50us,17个点用了1个小时,这样算下来,全部1024个点要近60个小时!3天啊?通常是这么慢么?

辛苦了,在你的指导下,10位理想DAC的verilog-a代码已经弄好了。现在又碰到新的问题,希望还能赐教。1.做的ADC是350khz,采样点先用较少的1024试一试。周期我选的是11,可以么?

总的相干采样公式是:3.8364/350=11/1024

2.仿真时间需要特别长,17个点用了1小时,总的1024个点要60个小时,正常么?

拜谢!

我这个过采样是不是太大了点?在论坛看到帖子,OSR=16,我这个近一百了

过采样率大只会fft仿真效果更好吧,如果你想看极限情况,就用奈奎斯特采样频率,周期数取512附近,信号输入在170K左右。

仿真快慢跟你的电路复杂度有关,也跟你仿真环境有关,我就得有个turbo或者aps选项,还有,你保存的信号不要选all-pub,选为selected,然后只看DAC输出波形就可以。这样速度可以快很多。

还有你的采样频率干嘛选350K啊,如果是做低功耗,我建议200K,这样的文献很多。

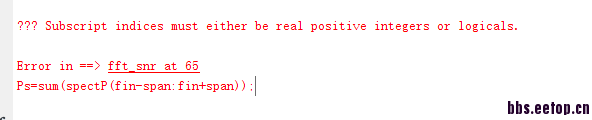

谢谢。加速的turbo和aps,我找找资料,自己先学习下。我仿了1个多小时,输出了17个点。现在用这17个点在matlab上做fft,算参数。在论坛里找了个matlab代码。但是仿真出错。看着跟美信的代码是一样的,不知道原因出在哪。能帮忙看一下么?

错误在红色部分。图片上显示的是错误类型。

符美信在出错段,相同的代码。

代码:

clear

load C:\Users\Administrator\Desktop\verilog3.txt%WaveScan保存的波形文件,文件必须以英文开头

A= verilog3;%将测量数据赋给A,此时A为N×2的数组

x=A(:,1);%将A中的第一列赋值给x,形成时间序列

x=x';%将列向量变成行向量

y=A(:,2);%将A中的第二列赋值给y,形成被测量序列

y=y';%将列向量变成行向量

%显示原始数据曲线图(时域)

subplot(1,1,1);

plot(x,y) ;%显示原始数据曲线图

xlabel('时间 (s)');

ylabel('被测变量y');

title('原始信号(时域)');

grid on;

format long;

%傅立叶变换

y=y-mean(y);%消去直流分量,使频谱更能体现有效信息

fclk=(length(x)-1)/(max(x)-min(x));%仪器的采样频率

numpt=length(y);%data.txt中的被测量个数,即采样个数

%If no window function is used, the input tone must be chosen to be unique and with

%regard to the sampling frequency. To achieve this prime numbers are introduced and the

%input tone is determined by fIN = fSAMPLE * (Prime Number / Data Record Size).

%To relax this requirement, window functions such as HANNING and HAMING (see below) can

%be introduced, however the fundamental in the resulting FFT spectrum appears 'sharper'

%without the use of window functions.

Doutw=y;

%Doutw=y'.*hanning(numpt);

%Doutw=y'.*hamming(numpt);

%Performing the Fast Fourier Transform

Dout_spect=fft(Doutw);

%Recalculate to dB

Dout_dB=20*log10(abs(Dout_spect));

%Display the results in the frequency domain with an FFT plot

figure; %建立图形

maxdB=max(Dout_dB(1:numpt/2));

%For TTIMD, use the following short routine, normalized to —6.5dB full-scale.

%plot([0:numpt/2-1].*fclk/numpt,Dout_dB(1:numpt/2)-maxdB-6.5);

%plot([0:30/2-1].*fclk/numpt,Dout_dB(1:30/2)-maxdB);

plot([0:numpt/2-1].*fclk/numpt,Dout_dB(1:numpt/2)-maxdB);

grid on;

title('FFT PLOT');

xlabel('ANALOG INPUT FREQUENCY (Hz)');

ylabel('AMPLITUDE (dB)');

a1=axis; axis([a1(1) a1(2) -120 a1(4)]);

%Calculate SNR, SINAD, THD and SFDR values

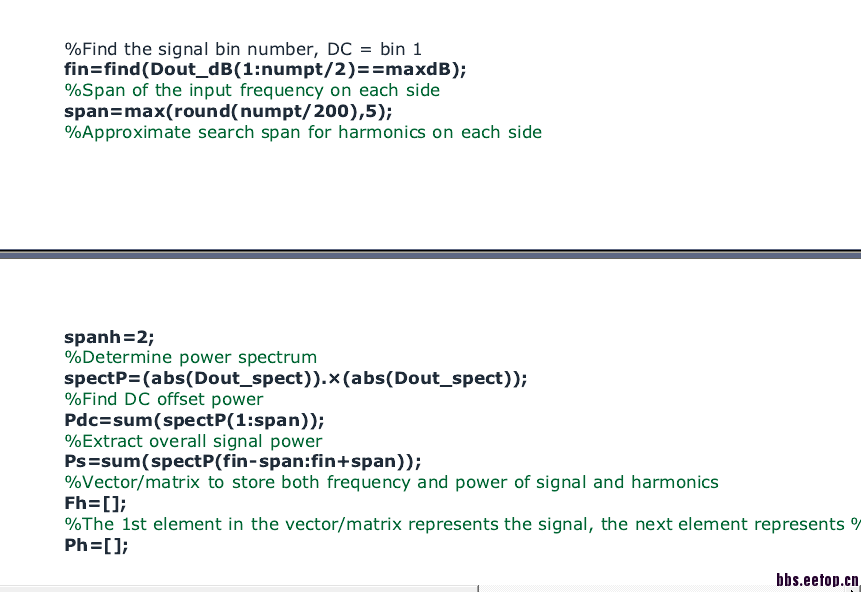

%Find the signal bin number, DC = bin 1

fin=find(Dout_dB(1:numpt/2)==maxdB);

%Span of the input frequency on each side

span=max(round(numpt/200),5);%span=max(round(numpt/200),5);

%Approximate search span for harmonics on each side

spanh=2;%spanh=2;

%Determine power spectrum

spectP=(abs(Dout_spect)).*(abs(Dout_spect));

%Find DC offset power

Pdc=sum(spectP(1:span));

%Extract overall signal power

Ps=sum(spectP(fin-span:fin+span));%出错行

%Vector/matrix to store both frequency and power of signal and harmonics

Fh=[];

%The 1st element in the vector/matrix represents the signal, the next element represents

%the 2nd harmonic, etc.

Ph=[];

%Find harmonic frequencies and power components in the FFT spectrum

for har_num=1:10 %har_num谐波总数

%Input tones greater than fSAMPLE are aliased back into the spectrum

tone=rem((har_num*(fin-1)+1)/numpt,1); %rem(x,y)x除以y的余数numpt(Number of Points)

if tone>0.5

%Input tones greater than 0.5*fSAMPLE (after aliasing) are reflected

tone=1-tone;

end

Fh=[Fh tone];

%For this procedure to work, ensure the folded back high order harmonics do not overlap

%with DC or signal or lower order harmonics

%har_peak=max(spectP(round(tone*numpt)-spanh:round(tone*numpt)+spanh));

%har_bin=find(spectP(round(tone*numpt)-spanh:round(tone*numpt)+spanh)==har_peak);

%har_bin=har_bin+round(tone*numpt)-spanh-1;

%Ph=[Ph sum(spectP(har_bin-1:har_bin+1))];

Ph=[Ph sum(spectP(har_num*(fin-1):har_num*(fin-1)+2))];

end

%Determine the total distortion power

Pd=sum(Ph(2:10)); %Pd总失真功率Ph(1) is fundamental harmonic谐波 power

%Determine the noise power

Pn=sum(spectP(1:numpt/2))-Ps-Pd;%Pn噪声功率Ps信号功率

format;%设置输出格式

SNR = 10*log10(Ps/Pn)%信噪比

SINAD=10*log10(Ps/(Pn+Pd)) % SINAD = 10*log10(Ps/(Pn+Pd))信号与噪声失真比

disp('THD is calculated from 2nd through 10th order harmonics');

SFDR=10*log10(Ph(1)/max(Ph(2:10)))%SFDR无杂散动态范围

ENOB = (SINAD-1.76)/6.02

disp('Signal & Harmonic Power Components:');

HD=10*log10(Ph(1:10)/Ph(1))

你出错是因为你把汉宁窗那句注释掉了

波形里面的tool下面没有“table”啊,只有calculate和results browser这两个选项,是怎么回事呢,还是我哪里搞错了,谢谢!

你好,理想DAC里面你说的vtran是转换中间点,这具体是个什么意思呢,谢谢?

就是高低电平的一半,理解为判决0和1的临界值

明白了,感激不尽

这是个好帖子啊

这个帖子回复真的很感人!

感觉小编还需要多学习,这个直接把DAC的模拟台阶画图,然后table取点就行了,复制到Windows下的txt里面,然后用matlab文件调用

DAC在ahdllib的库,你可以把8bit的代码改一下,改成10bit就能用了。其实数学分析,DNL和INL一般是很少有人去仿真,因为数据要求很大,4096也不会太精确。我建议你去跑斜坡信号,ADC的失码就可以看出来,如果各个模块很好的话,INL也不会差

thanks for your sharing