为什么Vsb>0引发背栅效应,而不考虑Vdb引发的体效应呢

Vsb>0,使得栅下耗尽层宽度增加,阈值电压增大,Vdb>0,应该跟Vsb>0引起的效应一样啊,为什么不考虑

帮顶一下!

因为漏端电压本来就是比源端电压大,体效应的产生是考虑源漏中电位更小的一个比sub电位高时产生的额外的对沟道的影响。

书上说的是Vth针对的是源端计算的,实际漏端的Vth由于体效应的影响也是增大的,但是不知道什么原因使得增大的这部分不考虑

什么书上讲到“漏端的Vth”?Vth的定义是表面反型电子浓度达到体内多子浓度时的栅极电压,但是实际应用中源漏之间电位是逐渐变化的,半导体表面势本来就不是平均分布的,严格的说从漏到源每一处达到强反型时对栅极电压的要求都不一样,那么对于你所说的体效应,不仅漏端,整个沟道各处都对“体效应“有影响,按照我的理解,体效应在VGS=0时不存在,只有VGS大于0时才需要考虑体效应。

第一:源漏是可以互换,源定义为提供载流子,漏定义为收集载流子。以NMOS为例的话Vd>Vs

第二:阈值电压的定义是栅下形成反型层时对应的电压值。

以NMOS为例,源端电位最较低,最容易反型,一旦Vgs>Vth栅下就会形成反型层,认为MOS开启了,所以只考虑源端。

至于你说的漏端Vth,在饱和区的话,个人认为你也可以认为是Vdb较大增加了漏端的Vth导致漏端关断。

同楼上的说的“严格的说从漏到源每一处达到强反型时对栅极电压的要求都不一样,那么对于你所说的体效应,不仅漏端”,所以我认为你还按照栅下是否形成反型层为标准的好。

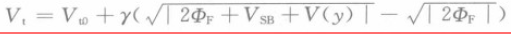

池保勇老师的模拟集成电路与系统P27,描述的沟道y点处的阈值电压为

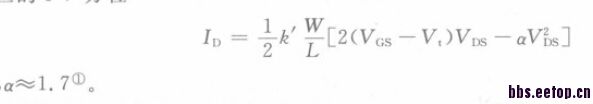

书中描述的考虑整个沟道引起的体效应之后的线性区沟道电流表达式:

I agree. “漏端的Vth” 会增大。 然后呢?会发生什么?另外,你有考虑过DIBL吗?

不懂你的point在哪?需要考虑什么?

既然整个沟道体效应对Vth都有影响,我们估算沟道电流以及计算Vdsat时,为什么不考虑这些影响呢?

........

就如你说的,drain只对“drain的Vth"有影响,对souce有什么影响?

Vth本身的定义确实是从gate到沟道,但是只要souce端附近通了,这个管子就通了,drain有什么影响?

drain端pinch off了,就pinch off了,电流由于经过从source到drain的加速,足以通过pinch off的drain端

你说的不错,体效应确实会对电流估算及Vdsat产生影响,但是这个影响的具体描述会使方程变得极其麻烦,你所看到的方程是最简单的描述,这里是基于一种假设,source端的Vth是最低的,即这一点导电能力最强,即最大的电流就是由他确定的,沟道内部即使pinch off,电子经过加速也能通过。但是you are right,drain会不会对电流产生影响?会!如何描述。?very complex!especially modern technology!

check “gradual channel approximation”, 你就知道I-V方程的推出做出了怎样的假设

Read the book “Operation and Modeling of the MOS Transistor”, you will understand how transistors work deeply !

原来这样,谢谢您的耐心解答,和您推荐的书

长知识了

恩,是个好问题,我帮你顶下