求救:cdce62005输出时钟频率总是比期望值低

时间:10-02

整理:3721RD

点击:

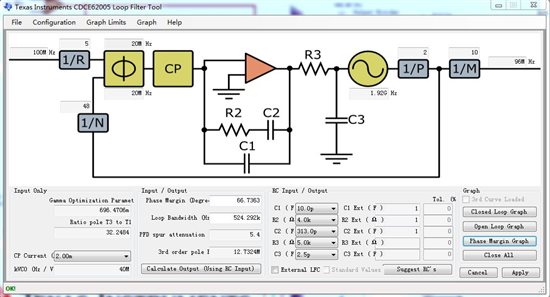

输入时钟100MHMz,用的RI;输出4路96MHz时钟,LVCMOS。用的TI的GUI软件计算的,如下图。现在的问题是:

1、输出时钟始终都只有82MHz,而且期望的输出频率越高比如120MH,160MHz,那么实际输出时钟偏差就越大;相反,期望频率越低,实际得出的频率反而会越好;如果不用VCO,而是直接输出分频,则输出时钟很正常;这是为什么啊?PLL Lock的引脚是低电平。

2、为什么GUI中VCO Calibration Word中的Calibrate不能用啊?

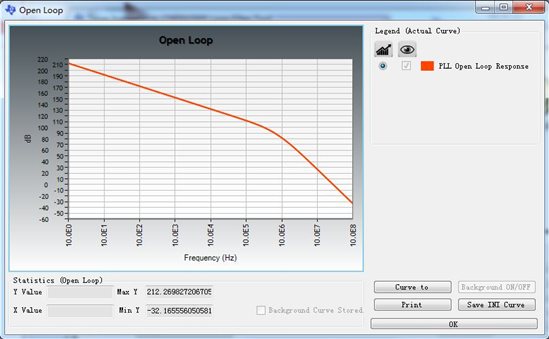

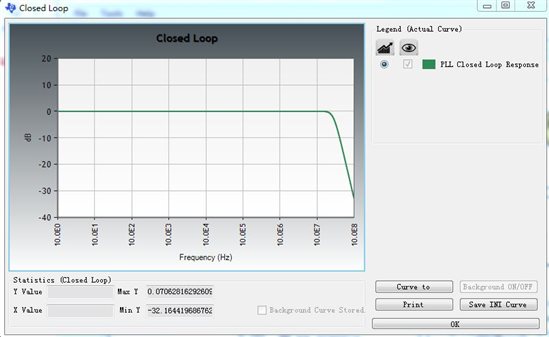

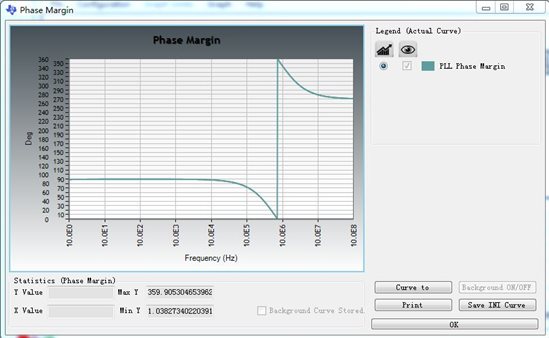

3、Loop Filter的开环、闭环、相位图对不对啊?对这一块不是很明白,电容电阻的值是自己慢慢试的,直到没出现警告为止。

4、如果输出频率锁定正常,那么寄存器8中的PLLLockPin位是不是应该是1?

Loop Filter的计算如下图:

开环、闭环、相位图如下:

PLL_LOCK = ?

用示波器量管脚是低电平,但是寄存器读出来又是1

寄存器读出来的也是0,表示没有锁定。上电后,我不是eeprom中load,而是通过spi口写。以下是写的寄存器的数值和顺序: 11060320 11060301 11060302 11060303 68860314 38100E45 04CE0566 BD90FDA7 80001808 80CE0566 84CE0566 80000808 80001808

寄存器8读出的值是80009A0

那要是将 输入频率 更改一下 试试呢?

例如:80M、66M、50M、40M、33M......?发表

你好,请检查你的配置流程,关于校准,初始配置应该是0,所以就是把初始的0写成1后再写回0。流程参考手册36页