LMK04828的输出分频比设置和输出时钟频率问题

请问:

我们遇到了,当配置输出分频比为1时,输出的时钟频率不对的问题。

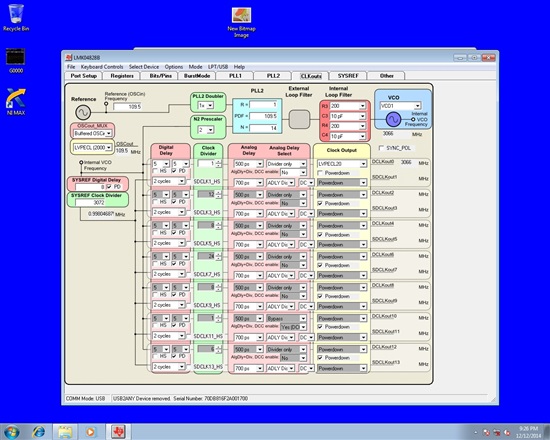

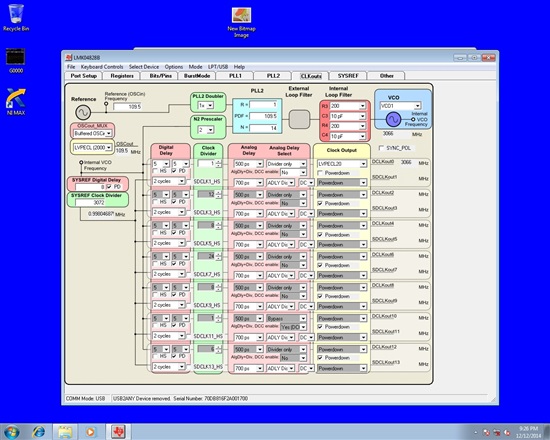

我们使用的是LMK04828的评估模块,通过CodeLoader配置。Analog Delay Select 选择的是Divider only。第二级VCO的输出频率锁定在3066MHz左右。如果配置输出分频比为2,倒是能得到1533MHz的时钟,这是正确的。如果配置输出分频比为1,输出频率则变为95MHz多,即32倍分频的结果。配置为其他分频比,都和配置成2是一样正确的,唯独1不行。

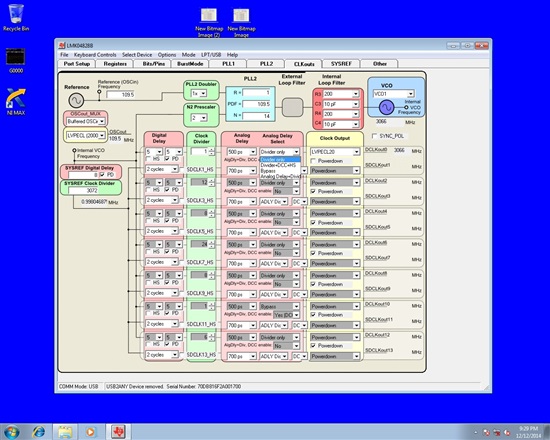

如果Analog Delay Select 选择的是bypass,倒是有3066MHz的时钟输出,但幅值明显小。

如果Analog Delay Select 选择的是Divider+DCC+HS,现象跟选择bypass一样。

应该怎么配置才能输出正常幅值的3066MHz的时钟呢?

尝试 其它组合 没有?

例如:VCO1=3000MHz

输出3066MHz时,幅值明显变小。

你用的是那个通道输出?EVM上不同通道的输出的电平不太一样,有LVDS和LVPECL的

你的参考是多少?

你好,你的描述与实际配置参数有些矛盾。

1。首先,分频比中没有1,最小是2;因此如果你在clock output 选择divider only那么可定不可能直接出3066M;如下

2。Analog Delay Select 也不是用来选择Divider only的,而是用clock output选择 bypass;应该可以出来。如果幅度不对,请发你的测试图形和使用的设备型号

DCLKout0,EVM上这个通道是默认端接成LVPECL的,输出电平配置也的确是LVPECL20。

这一路差分线在EVM上有两个SMA接口,一个用50ohms匹配负载端接,另一个连接50ohms输入阻抗的示波器进行测量。可保证测量链路有18GHz的带宽。

4380.3066.tif

这是设置分频比为1时的结果,如主贴所述。

6787.1533.tif

这是设置分频比为2时的结果,如主贴所述。

7651.bypass.tif

这是设置bypass时的结果,如主贴所述。

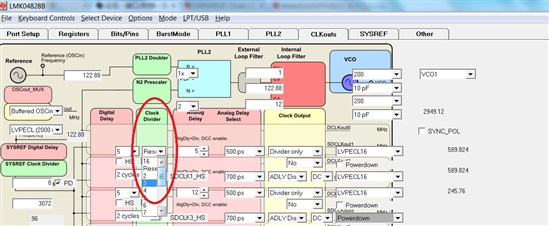

这是分频比为1的配置。

你好,可能你的软件界面是错乱的,导致选项顺序错误。在我这里,配置都是可以的。并且,这样配置也被datasheet所允许。请看:

1. 分频比为1的配置

2. 分频比为2的配置

3. 在这里可改为bypass。

这一级PLL的鉴相频率是109.5MHz,所以锁在2956.5MHz试过,一样的,请看其他楼里的测试图

LVPECL端节匹配用示波器探头测量可能无法正确测量功率,建议你用使用频谱仪或用LVDS测试;

有关divider的1设置请参看手册58页注释1:

1) Not valid if DCLKoutX_MUX = 0, Divider only. Not valid if DCLKoutX_MUX = 3 (Analog Delay + Divider) and DCLKoutX_ADLY_MUX =

0 (without duty cycle correction/halfstep).