lmx2541SQ2690E配置出来的时钟频率有偏差,且ld引脚配置后一直是0

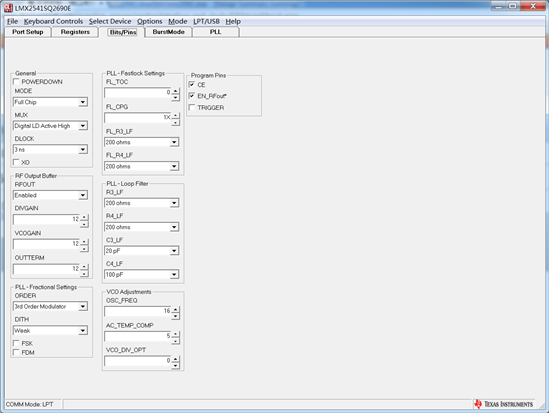

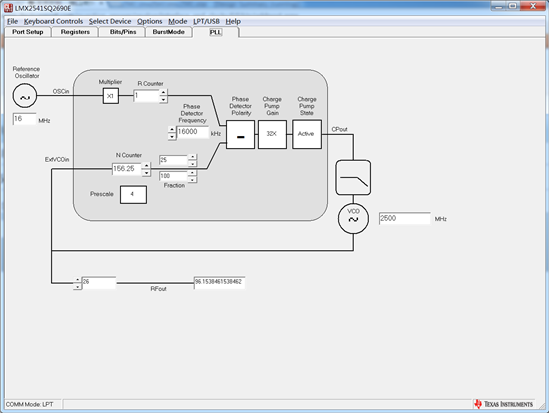

这个是我利用codeloader配置的,导出寄存器值,利用fpga写入,出来的时钟有几Mhz的偏差,调节R3R4C3C4参数会使最终输出频率有一定改变,但是都不是我想要的100Mhz。

请问这配置有什么问题,ld引脚为何没有锁定。

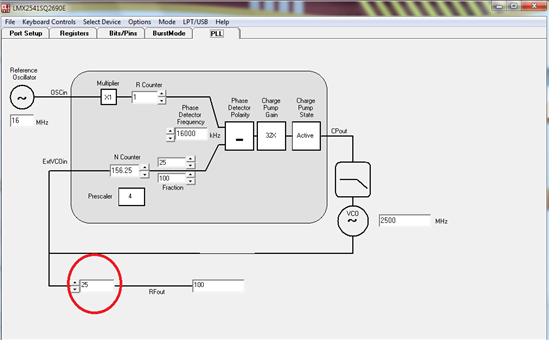

可以输出100Mhz的啊。把分频系数改成25就好了。

你好,谢谢你的回答,这个地方 是我截图的时候不小心点错了,我的实际分频系数是25.

这个问题感觉是因为没有锁住,LD引脚也说明了这个问题。

想请问下有没有可能是因为FPGA的配置时序问题呢?但是感觉时钟能够输出了,时序应该是正确的

你好,如你的LD测试结果没有锁定。

如果要验证时序很简单,可以手动设置LD的状态,如果LD输出跟随你的设置高低变化,则证明uWIRE工作正常。

MUX[3:0] -- Multiplexed Output for Ftest/LD Pin

下一步可以设置为N divider输出或R divider输出看是否和预想的一致

详见手册 page 45: 9.6.1.8.5

你好,我改变了mux后,ld确实是改变了,如把mux设置成低有效,那么ld就是配置完为高,虽然还是没有锁定。

这就不知道什么问题了,看上去时序应该没问题。

请问下有没有FPGA的代码可以分享下,只需要输出单一频率信号。

谢谢。

那说明配置是进去了接口对的,时序上应该没有问题。

请你将mux配置为N Divider和N Divider / 2

以及R Divider和R Divider / 2

请给出在这四个配置下mux输出信号的频率分别 是多少,波形是否正常,谢谢

你好,我试了下上述四种模式下的输出,N和N/2模式下输出频率都为105.7左右,R和R/2模式下,时钟没有输出。手册上说这个引脚的配置是可能影响信号的。

LD引脚输出在这些模式下,是一直显示对应N或者R信息的吗?我抓到的情况是只有配置时序中才会有ld引脚变化,我不知道Ld状态是不是对的,怎么和N或R信息对应起来。之后都是保持高或低状态。

配置后就应该有相应输出divider后的频率,你的测试结果与前面的配置截图不符,很大可能性是参考信号没有被正确识别而导致锁相环没有锁定。请测试参考输入信号的幅度和频谱,谢谢!

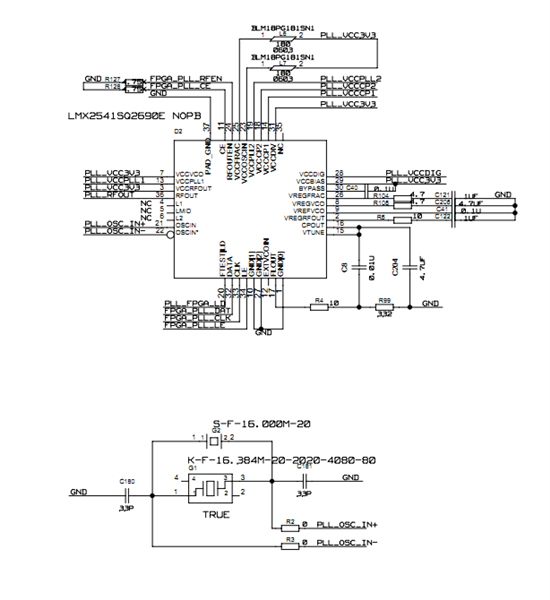

你好,我用示波器测了下输入信号,差分一端为正弦波,均值大概是1.5V,峰峰值大概是1V,另一端为0,频率是正确的16MHz。这样说明输入信号应该是对的,还是配置的问题。

你所说的差分信号均值一端均值1.5V是指共模吗,源是哪儿来的,是在管脚上测得吗?你有做交流耦合吗?把原理图贴上来看下吧?

谢谢你的回复。

输入是晶振给的。

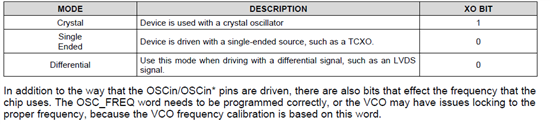

你输入是Crystal, 参考输入模式是否有设置XO=1?从你上面的配置图看是没有的。

另外这个晶振输出的信号比较怪,你可以先设置为单端,外接VCXO交流耦合测试下是否正常锁定来排除问题。

最后更换了输入信号晶振,从smb输入差分信号,输入频率正确且一直锁定。

是的,应该就是晶振的问题。

你好,抱歉再打扰你。

之前用晶振25M配置出锁定的100M信号后,想通过信号源给25M也能配置出来,通过信号源给SMB在给PLL芯片,出来的频率有偏差,而且没有锁定。

请问这是什么原因呢?我把信号源给的信号的幅度和偏置基本调成和晶振一致。信号源不管是给方波还是正弦波都不对。

debug的套路还是和我前面的方法一样,首先mux配置为R或R/2,看下参考是否正确识别。如果没有,看下交流匹配是否正确,端口设置是否正确。