NC和VCS在编译时出现不同的结果

- `timescale 1ns/10ps

- program test_dis(input [7:0] data);

- initial

- $display("@%0t, PROGRAM : data = %d", $time, data);

- endprogram

- module tb();

- reg [7:0] data;

- reg clk;

- initial

- begin

- #0clk = 0;

- data = 0;

- #20 $stop;

- end

- always #5 clk = ~clk;

- always @ (negedge clk)

- begin

- data <= $random%128;

- $display("@%0t, DISPLAY : data = %d", $time, data);

- end

- test_dis u1(data);

- endmodule

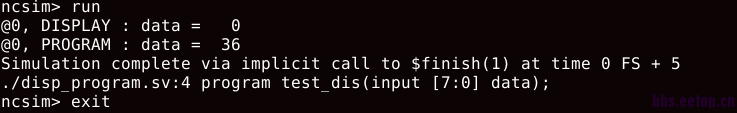

代码如上,利用NC编译,可以得到相应的结果:(PS:如何让仿真时间不在0时刻停止呢?为什么会隐形调用finish呢?)

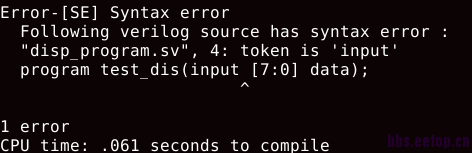

但是利用VCS编译的时候,会有如下error:

只能说明,VCS的语法检查更严格。尽管仿真结果都非预期。

用 program test_dis(input bit[7:0] data); 试试?

一样的有误。logic一样的会报错。

Sorry, I did not see your code carefully before. Yes, SV does supports default bit argument declaration

And I also checked your code again, it should not be any difference with IRUN and VCS. Actually, it is proved in my site.

The reason why your code did not run is that you used PROGRAM structure but you did not put any timing procedure inside it. The whole testbench will finish after the last initial block of PROGRAM is run. So it means you code will always be done at #0. If you put the code #20 stop inside the initial block of PROGRAM. You problem can be resolved.

工具不同,选项也不一样!如果纯粹为了检查语法及综合性,最好用专门的工具!VCS 和 NC只是一个simulator而已!

是的,今天我也发现了这个原因。软件和硬件的描述思维方式确实不一样啊

systemverilog中,program为主进程,当program执行完毕时,会自动finish。你在0ps停止仿真,是因为你program中的initial中,只有1个display它结束你的仿真就结束了。

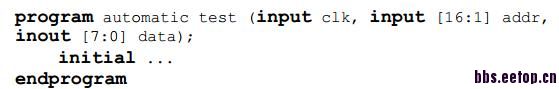

你vcs用的什么版本的?不同版本的仿真器或者不同的仿真器,对sv的语法结构实现的程度和认可度是不一样的,不能因为这个就说什么仿真器语法检查更为严格。我在vcs2012.09的手册中,看到如下结构:

说明vcs是完全支持这个结构的。

拿ius9.2来说,它还无法支持program带有lifetime参数呢,你能说它语法检查更严格吗?