关于transition、fanout和capacitance的violation在Placement阶段如何修

目前在做Placement,做了place_opt后,report_constraint报出了许多transition、capacitance和fanout的violation,虽然看了许多了帖子,但是面对具体问题仍不知该如何解决。

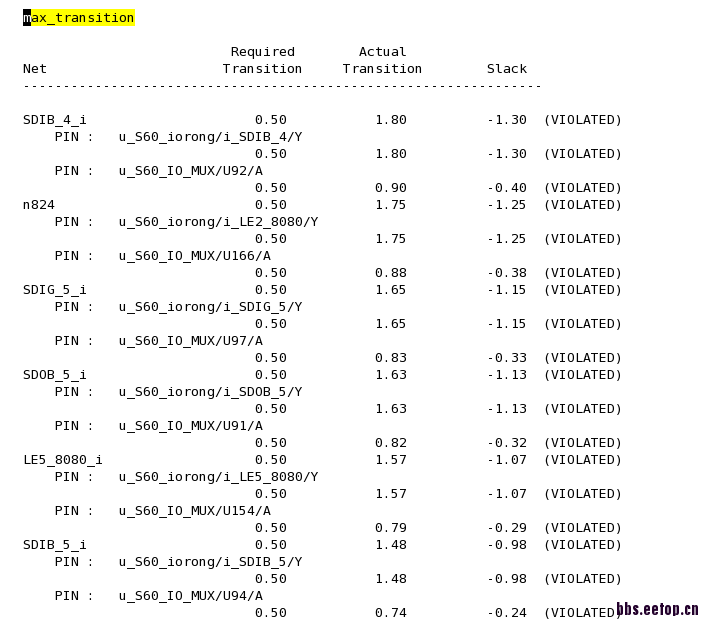

首先是transition,有三种:一种是PAD输出端到逻辑门输入端的路径,第二种是逻辑门到逻辑门的路径,第三种是逻辑门到sram的pin端的路径。情况如图所示,但哪些需要处理哪些不需要关注,及该具体如何处理,不是特别清楚。

第二是fanout,如下图

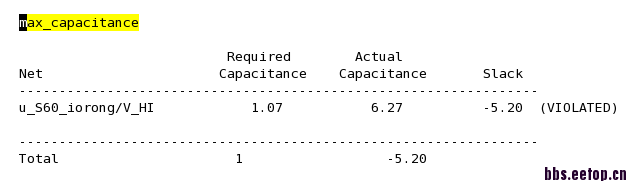

第三是capacitance,如下图,发现这是个TIEHI的输出端连到了所有IO的IE(input_enable)和PD(weak pull down)端,不知道是不是我之前的某个步骤有错造成的。

因为是初学ICC,卡在这里感觉很困惑,希望大侠能给于一些提示或者指导,非常感谢!

看看place之前是否设置了set_ideal_network/set_dont_touch 这些语句,有的话

是有可能造成你drc不修的原因的,

通常place阶段除了cts 还有highfanout不修,即drc disabled ,其他net的trans/cap/fanout都会

自动修

fanout不用太care,只要trans/cap ok就行

iopad输出到外面的可以不看看, port外面的设置通常比较悲观

tie net cap问题可以不看,这个你后面connect_tie_cells 会修掉的

嗯,多谢版大的解惑!我想我明白了,我先试试看先,不明白的再向您请教!

后面的 connect_tie_cells 为什么可以修掉 tiecell 的max_cap违例呢

我从place加进来tiecell时 就有 tiecell的 max_cap违例,但一直到最后还是有这个违例 (中间阶段也用了几次 connect_tie_cell的命令)

max_capacitance

RequiredActual

NetCapacitanceCapacitanceSlackScenario

-----------------------------------------------------------------

TIEL_HVT!U213_net34.49630.12-595.63(VIOLATED) func_wc_cmax

TIEL_HVT!U200_net34.49580.90-546.41(VIOLATED) func_wc_cmax

TIEL_HVT!U183_net34.49580.45-545.96(VIOLATED) func_wc_cmax

TIEL_HVT!U250_net34.49571.51-537.02(VIOLATED) func_wc_cmax

TIEL_HVT!U164_net34.49569.72-535.23(VIOLATED) func_wc_cmax

TIEL_HVT!U237_net34.49567.84-533.35(VIOLATED) func_wc_cmax

TIEL_HVT!U212_net34.49562.72-528.23(VIOLATED) func_wc_cmax

TIEL_HVT!U190_net34.49560.99-526.50(VIOLATED) func_wc_cmax

TIEL_HVT!U163_net34.49547.13-512.64(VIOLATED) func_wc_cmax

TIEL_HVT!U204_net34.49537.72-503.23(VIOLATED) func_wc_cmax

而且违例比较大,这个如何解决呢! 先谢谢小编啦

大神,我最近做placement时也遇到了好多tie cell net的max_cap违例,请问你后来是怎么解决的呢?万分感谢!

我遇到过这个问题,只记得ICC有个变量需要打开才能看到tie_high/tie_low的max_cap违背,ICC工具才会去修。不过,我刚才一直没找到,也许你可以按这个思路去找找。

您好,这个您找到了吗?我找了好久也没找到

请问你的tie单元的max capacitance设置的多大啊?lib里面的一半吗?