请教下set_driving_cell 和set_input_transition的区别

set_driving_cell以后,它与input pin之间的transition是由工具自己算出来的,可大可小

set_input_transition就是不让工具算,强加一个,自然timing会变好,但不一定是真实的

陈小编,我看你原来说过,对输入端加约束的话,一般就用set_driving_cell (set_input_transition也有用的,但不多见),因为set_driving_cell 更接近于真实环境,那如果用set_driving_cell 后,后端调入网表setup违反很大,让前端修违反,该怎么修呢?

先要找原因,不能简单地推给前端

可能这个工程用的130nm的吧,以前用的都是高工艺,后端说以前调入网表没有这么大的违反,这次这个直接调入网表setup违反就有100,他们没法往下做,让前端修。我想问下,用了set_input_transition 设置理想值,有没有什么不确定因素,因为以前都是用的set_driving_cell 。

推荐:block : set_driving_cell

chip:set_input_transition

应该是set_drive_cell后,会有一些不确定因素,会随着loading变化

set_transition后,一切会变得简单

好的,多谢陈小编!

学习了,谢谢高手们

set_driving_cell 会考虑ocv 这些东西,更准些 ,

input transition比较简单,适合chip io pad约束,

studying

看CTS的时候UG有这么说如果clock root是个input port,没有IO PAD,则指定set_driving_cell

如果clock root是个IO pad cell,则精确指定set_input_transition

我在DC里面约束的是driving cell,floorplan的时候加了IO pad,应该指定transition time?

如果是transition time,一般经验值是多少,我的工艺是180,频率50M

如果脚本中同时写了set_driving_cell和set_transition_time,是两者叠加呢,还是以后读入的为准?

这种情况以后读入的为准。

请问这个有什么道理或原因吗?

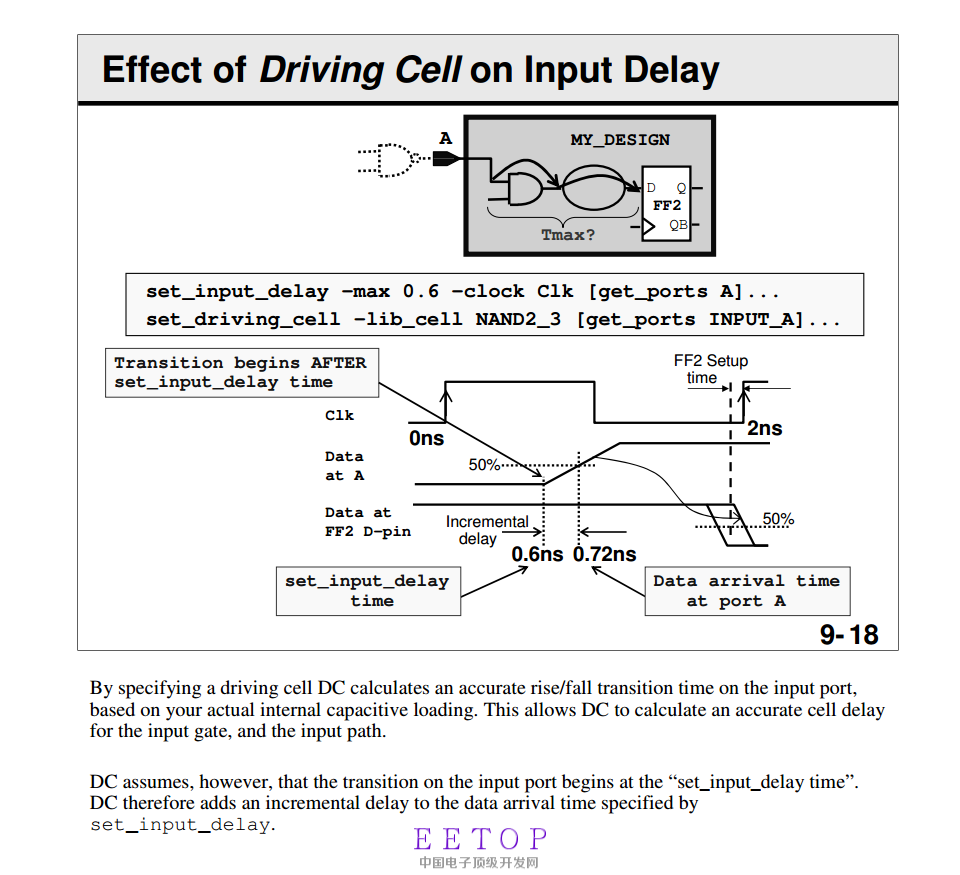

DC workshop - student guide 200703这里对set_driving_cell做了清楚的说明:

学习学习~

学习了,谢谢高手!

学习了!

學習一下了,謝謝~