求助關於NCX建cell library的問題

解了很久但不知道問題在哪邊,請高手幫忙

另外想特別請問acq是怎麼樣的檔案格式呢? 記錄了什麼資訊?

謝謝

----------------------------------------------------------

Sat Aug 31 21:09:27 2013

checking job status... 0 nets queued, 1 jobs running, 1 pending, 0 done.

Sat Aug 31 21:09:58 2013

checking job status...

Warning: Fail to run job for /home/Lab333a/Desktop/NCX_problem_x64/ncx_ERFF/sim_dir/lib/erff_slow_ncx/ERFF/mCK_CK_0000f/mCK_CK_0000f.sp

Warning: Fail to run job for /home/Lab333a/Desktop/NCX_problem_x64/ncx_ERFF/sim_dir/lib/erff_slow_ncx/ERFF/dERFF_0029/dERFF_0029.sp

done.

job [0] [11 simulations]

Warning: Recheck /home/Lab333a/Desktop/NCX_problem_x64/ncx_ERFF/sim_dir/lib/erff_slow_ncx/ERFF/mCK_CK_0000f/mCK_CK_0000f.acq [1].

netlist: /home/Lab333a/Desktop/NCX_problem_x64/ncx_ERFF/sim_dir/lib/erff_slow_ncx/ERFF/mCK_CK_0000f/mCK_CK_0000f.sp

No .acq file detected

Error: Simulating netlist [/home/Lab333a/Desktop/NCX_problem_x64/ncx_ERFF/sim_dir/lib/erff_slow_ncx/ERFF/mCK_CK_0000f/mCK_CK_0000f.sp] fails for cell ERFF. (NCXFL-5)

Warning: Recheck /home/Lab333a/Desktop/NCX_problem_x64/ncx_ERFF/sim_dir/lib/erff_slow_ncx/ERFF/mCK_CK_0000r/mCK_CK_0000r.acq [1].

可能是你的路径或者是网表问题···做好把启动文件也帖上来····

下面是我所寫的config檔以及netlist

麻煩了,謝謝

---------config file-------------

set model_file cmn90g_3d3_lk_v2d0.l

set netlist_dir ./netlists

set netlist_suffix .sp

set template_suffix .opt

#set simulator_type hspice

set simulator_exec /usr/cad/synopsys/hspice/cur/hspice/bin/hspice64

set output_library erff_slow_ncx.lib

set input_template_dir ./template

set simulation_dir./sim_dir

set work_dir./my_work

set farm_type nofarm

#True for produce template files, False for produce real delay model

set templates false

#enable AutuFunction

#set auto_function true

#some additional setting

#set hspice_server true

set timingtrue

set powertrue

set nldmtrue

set nlpmtrue

set constrainttrue

set design_rules true

set ccs_timingtrue

set ccs_powertrue

set driver_waveform_to_library false

set log_file erff_slow.log

set test_simulator false

set max_jobs 1

------------------------------------

--------netlist file---------------

.subckt erff q d ck late vdd vss

MM1DbDvdd vdd pch l=100nch w=360n

MM2DbDvss vss nch l=100nch w=120n

MM3D2Dbvdd vdd pch l=100nch w=360n

MM4D2Dbvss vss nch l=100nch w=120n

MM5CKbCKvdd vdd pch l=100nch w=360n

MM6CKbCKvss vss nch l=100nch w=120n

MM7DbCKn1vdd pch l=100nch w=360n

MM8DbCKbn1vss nch l=100nch w=120n

MM9n2n1vdd vdd pch l=100nch w=360n

MM10n2n1vss vss nch l=100nch w=120n

MM11n3n2vdd vdd pch l=100nch w=360n

MM12n3n2vss vss nch l=100nch w=120n

MM13n3CKbn1vdd pch l=100nch w=360n

MM14n3CKn1vss nch l=100nch w=120n

MM15n2Latenmvdd pch l=100nch w=360n

MM16n2Lateb nmvss nch l=100nch w=120n

MM17DLateb nmvdd pch l=100nch w=360n

MM18DLatenmvss nch l=100nch w=120n

MM19nmCKbn4vdd pch l=100nch w=360n

MM20nmCKn4vss nch l=100nch w=120n

MM21n5n4vdd vdd pch l=100nch w=360n

MM22n5n4vss vss nch l=100nch w=120n

MM23n6n5vdd vdd pch l=100nch w=360n

MM24n6n5vss vss nch l=100nch w=120n

MM25n6CKn4vdd pch l=100nch w=360n

MM26n6CKbn4vss nch l=100nch w=120n

MM27Dbn1Lavdd pch l=100nch w=360n

MM28Dbn2Lavss nch l=100nch w=120n

MM29D2n2Lavdd pch l=100nch w=360n

MM30D2n1Lavss nch l=100nch w=120n

MM31Lateb CKvdd vdd pch l=100nch w=360n

MM32nx1CKvss vss nch l=100nch w=120n

MM33Lateb Lanx1 vss nch l=100nch w=120n

MM34LateLateb vdd vdd pch l=100nch w=360n

MM35LateLateb vss vss nch l=100nch w=120n

MM36Qn5vdd vdd pch l=100nch w=360n

MM37Qn5vss vss nch l=100nch w=120n

.ends

你的这个config是ncx的运行脚本,而不是opt文件····还有你这个网表是前仿的啊····特征化没意思啊······

以下是我的opt file,不好意思之前沒看懂您說得啟動文件是指opt,才貼成ncx運行腳本,

而這個opt file是我利用lib檔轉出各個cell的opt之後,再找出類似的來作修改,

但因為我想做的cell找不到非常類似的opt可以模仿,所以蠻多部份是我自己撰寫,

可能有許多錯誤,還請幫忙,謝謝。

另外想請問 "前仿" 的意思是? 為何此cell特徵化沒意思?

我的想法是想將此cell寫成lib檔之後,放到design compiler中作合成的時候使用,

感謝指教。

----------------------------------------------

cell_footprint : erff ;

area : 15.5232000 ;

cell_leakage_power : 52230.9600000 ;

ncx_ff : true ;

ncx_create_arcs : D D internal_power states default ;

ncx_create_arcs : CK CK internal_power states D\

!D ;

ncx_create_arcs : * * leakage_power states \

"!D & !CK & !Q "\

"!D & !CK &Q "\

"!D &CK & !Q "\

"!D &CK &Q "\

" D & !CK & !Q "\

" D & !CK &Q "\

" D &CK & !Q "\

" D &CK &Q " ;

statetable "CK D" "La" {

table :"H L/H : - : H,\

H -: - : N,\

L -: - : L" ;

}

#ncx_condition {

#ncx_condition_cell_name: DFFR* ;

#ncx_condition_model : cell ;

#ncx_auto_function_pin_pattern : q_pin Q qn_pin QN ;

#}

pin D {

direction : input ;

ncx_internal_power_rise_input_transition_time_index : 0 ;

ncx_internal_power_fall_input_transition_time_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

}

pin CK {

direction : input ;

clock : true ;

max_transition : 0.5120000 ;

min_pulse_width_high : 0.1514550 ;

min_pulse_width_low : 0.1076420 ;

ncx_internal_power_rise_input_transition_time_index : 0 ;

ncx_internal_power_fall_input_transition_time_index : 0 ;

ncx_active_edge : R ;

ncx_clock : true ;

}

pin La {

direction : internal ;

internal_node : La ;

}

pin Late {

direction : output ;

function : " CK & La " ;

}

ncx_multiple_descriptor {

# flip-flop path to Q:

ff "IQ1" "IQN1" {

clocked_on : CK ;

next_state : D ;

}

# latch path to O:

latch "IQ2" "IQN2" {

enable : CK ;

data_in : D ;

}

}

/* must use internal pins to capture ff values for use in function */

pin INT1 {

direction : internal ;

function : IQ1 ;

}

pin INT2 {

direction : internal ;

function : IQ2 ;

}

pin Q {

direction : output ;

state_function : "(!La & INT2) * (La & INT1)" ;

max_capacitance : 0.0547550 ;

ncx_internal_power_rise_input_transition_time_index : 0 ;

ncx_internal_power_fall_input_transition_time_index : 0 ;

ncx_internal_power_rise_total_output_net_capacitance_index : 17 ;

ncx_internal_power_fall_total_output_net_capacitance_index : 17 ;

ncx_internal_power_rise_equal_or_opposite_output_net_capacitance_index : 0 ;

ncx_internal_power_fall_equal_or_opposite_output_net_capacitance_index : 0 ;

ncx_rising_edge_rise_input_net_transition_index : 0 ;

ncx_rising_edge_fall_input_net_transition_index : 0 ;

ncx_rising_edge_rise_total_output_net_capacitance_index : 2 ;

ncx_rising_edge_fall_total_output_net_capacitance_index : 2 ;

}

pg_pin VDD {

voltage_name : VDD ;

pg_type : primary_power ;

}

pg_pin VSS {

voltage_name : VSS ;

pg_type : primary_ground ;

}

我也發生同樣的問題, 求解~

小编你好,我公司专注于开发标准单元库 IO库,SRAM

多家客户用我们的库已量产

如有需要可与我联系

opt还有sensitization部分,请问你是如何处理的

我也遇到相同的問題~

netlist:/......................................./tZ_A1_0000f.sp

no output .lis file detected--simulator has not run

Error: Simulating netlist[/............../tZ_A1_0000f.sp]fails for cell AN2D1.(NCXFL-5)

ncx已轉出.sp檔~感覺上是要開始run spice抓delay的時候無法執行~

spice路徑及model路徑都寫在ncx要run的config內了~不知為何還是這樣!

请问,运行ncx脚本的命令是“ncx -f file1”这样的格式吗?脚本文件就是文档吧?

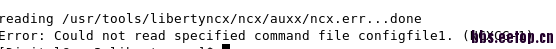

我这样做会弹出错误,1.png)

小编这个问题还记得怎么解决吗

您好,我现在也遇到您这个问题了,您现在解决了吗?求助啊,完全没思路,看manual也没看出来