求助大神,跑ncx时提示错误:subckt INV1 not defined in netlist

时间:10-02

整理:3721RD

点击:

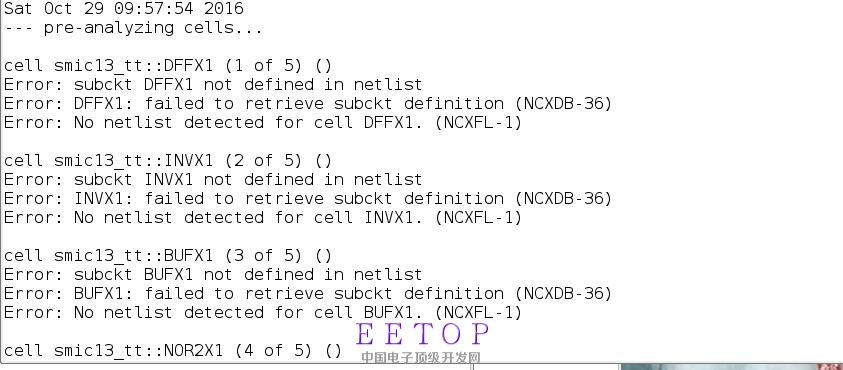

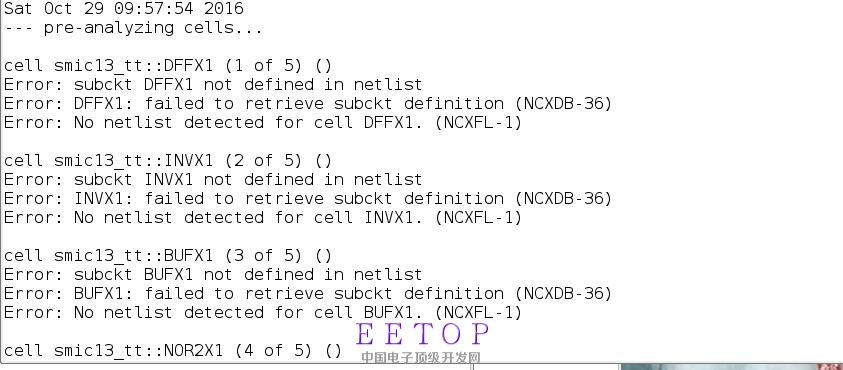

各位大神好,在下要做标准单元库,现在用ncx来提取.lib文件,但一直提示“subckt INV1 not defined in netlist”。根据提示应该是网表文件有问题,但我用的应该是带寄生参数的网表啊。弄了好几天一直是这样都快崩溃了,我附上我的.config文件和.sp文件,请大神们帮忙看下到底哪里有问题?感谢不尽。错误提示截图:

INVX1.sp网表文件

*

*

*LINUXSun Sep 25 19:41:39 2016

*

*

*

*PROGRAMadvgen

*

*Name: advgen - Quantus QRC - (64-bit)

*Version: 15.1.4-s005

*Build Date: Fri Nov 20 15:19:16 PST 2015

*

*HSPICE LIBRARY

*

*

*

.SUBCKT INVX1 A Y VSS VDD

*

*

*caps2d version: 11

*

*

*TRANSISTOR CARDS

*

*

MNM0

Y#1

A#7

VSS#1

VSS

n15ll

L=1.3e-07

W=3.5e-07

+ AD=1.099e-13

AS=1.701e-13

PD=1.328e-06

PS=2.28e-06

+ NRD=0.897143 NRS=1.38857 sa=2.3e-07 sb=3.14e-07 m=1 sd=0 nf=1

MPM0

Y#2

A#3

VDD#1

VDD

p15ll

L=1.3e-07

W=8e-07

+ AD=2.512e-13

AS=2.736e-13

PD=2.228e-06

PS=3.18e-06

+ NRD=0.3925 NRS=0.4275 sa=2.3e-07 sb=3.14e-07 m=1 sd=0 nf=1

*

*

*RESISTOR AND CAP/DIODE CARDS

*

Re_3_2

A#3

A#4

17.9630

$poly

Re_2_1

A#4

A#5

13.7139

$poly

Re_1_1

A#6

A#7

7.6114

$poly

Re1

A#5

A#9

9.4525

$poly

Re2

A#9

A#1

3.0401

$poly

Re3

A#9

A#6

22.8869

$poly

Rd1

A

A#1

17.0166

$metal1

Rd2

Y

Y#1

18.3271

$metal1

Rd3

Y

Y#2

9.4577

$metal1

Rd4

VDD

VDD#1

8.5000

$metal1

Rd5

VSS

VSS#1

8.5000

$metal1

*

*

*

*CAPACITOR CARDS

*

*

C_1

A

VSS

1.90867E-17

C_2

Y

VSS

2.48541E-17

C_3

A

VDD

6.05056E-18

C_4

Y

VDD

5.84458E-18

C_5

A#1

VSS

5.85054E-17

C_6

A

Y

3.00916E-17

C_7

Y#1

VSS

4.0367E-17

C_8

VDD#1

VSS

4.02275E-17

C_9

A#1

VDD

1.75732E-18

C_10

A#5

VSS

7.00429E-19

C_11

Y#2

VDD

5.069E-17

C_12

A

VSS#1

6.82701E-18

C_13

Y

A#1

1.18617E-17

C_14

A#4

VDD

3.11162E-17

C_15

A

VDD#1

8.00122E-18

C_16

A#5

VDD

1.36375E-17

C_17

Y

A#4

3.37984E-18

C_18

Y

A#5

7.74833E-18

C_19

Y#1

A#1

5.33416E-18

C_20

VSS#1

A#1

1.33311E-17

C_21

VDD#1

A#1

1.32804E-17

C_22

VSS#1

Y#1

3.39784E-17

C_23

Y#2

VDD#1

3.77889E-17

C_24

VDD#1

A#4

5.22662E-17

C_25

Y#2

A#4

9.12325E-17

C_26

Y#1

A#7

6.11434E-17

C_27

A#7

VSS

3.31047E-17

C_28

VSS#1

A#7

5.13338E-17

C_29

VSS

0

4.01639E-20

C_30

VSS#1

0

8.33704E-20

C_31

VDD#1

0

8.33704E-20

C_32

Y#2

0

4.01639E-20

*

*

.ENDS INVX1

.config文件

set model_file /home/peter/LibraryFile/smic13/models/hspice/cis013_ll_fsi_v1p0.mdl

set model_file /home/peter/LibraryFile/smic13/models/hspice/cis013_ll_fsi_v1p0_nmoscap.ckt

set model_file /home/peter/LibraryFile/smic13/models/hspice/cis013_ll_fsi_v1p0_res.ckt

set netlist_suffix .sp

set template_suffix .opt

set netlist_dir ./source

set simulator_exec /opt/synopsys/HSPICE_2015_06/hspice/bin/hspice64

set input_template_dir ./Template

set output_library ./Output/smic13_tt.lib

set work_dir work

set farm_type nofarm

set templates false

set timing true

set power true

set nldm true

set nlpm true

set design_rules true

set ccs_timing true

set ccs_power true

set log_file ncx.log

INVX1.sp网表文件

*

*

*LINUXSun Sep 25 19:41:39 2016

*

*

*

*PROGRAMadvgen

*

*Name: advgen - Quantus QRC - (64-bit)

*Version: 15.1.4-s005

*Build Date: Fri Nov 20 15:19:16 PST 2015

*

*HSPICE LIBRARY

*

*

*

.SUBCKT INVX1 A Y VSS VDD

*

*

*caps2d version: 11

*

*

*TRANSISTOR CARDS

*

*

MNM0

Y#1

A#7

VSS#1

VSS

n15ll

L=1.3e-07

W=3.5e-07

+ AD=1.099e-13

AS=1.701e-13

PD=1.328e-06

PS=2.28e-06

+ NRD=0.897143 NRS=1.38857 sa=2.3e-07 sb=3.14e-07 m=1 sd=0 nf=1

MPM0

Y#2

A#3

VDD#1

VDD

p15ll

L=1.3e-07

W=8e-07

+ AD=2.512e-13

AS=2.736e-13

PD=2.228e-06

PS=3.18e-06

+ NRD=0.3925 NRS=0.4275 sa=2.3e-07 sb=3.14e-07 m=1 sd=0 nf=1

*

*

*RESISTOR AND CAP/DIODE CARDS

*

Re_3_2

A#3

A#4

17.9630

$poly

Re_2_1

A#4

A#5

13.7139

$poly

Re_1_1

A#6

A#7

7.6114

$poly

Re1

A#5

A#9

9.4525

$poly

Re2

A#9

A#1

3.0401

$poly

Re3

A#9

A#6

22.8869

$poly

Rd1

A

A#1

17.0166

$metal1

Rd2

Y

Y#1

18.3271

$metal1

Rd3

Y

Y#2

9.4577

$metal1

Rd4

VDD

VDD#1

8.5000

$metal1

Rd5

VSS

VSS#1

8.5000

$metal1

*

*

*

*CAPACITOR CARDS

*

*

C_1

A

VSS

1.90867E-17

C_2

Y

VSS

2.48541E-17

C_3

A

VDD

6.05056E-18

C_4

Y

VDD

5.84458E-18

C_5

A#1

VSS

5.85054E-17

C_6

A

Y

3.00916E-17

C_7

Y#1

VSS

4.0367E-17

C_8

VDD#1

VSS

4.02275E-17

C_9

A#1

VDD

1.75732E-18

C_10

A#5

VSS

7.00429E-19

C_11

Y#2

VDD

5.069E-17

C_12

A

VSS#1

6.82701E-18

C_13

Y

A#1

1.18617E-17

C_14

A#4

VDD

3.11162E-17

C_15

A

VDD#1

8.00122E-18

C_16

A#5

VDD

1.36375E-17

C_17

Y

A#4

3.37984E-18

C_18

Y

A#5

7.74833E-18

C_19

Y#1

A#1

5.33416E-18

C_20

VSS#1

A#1

1.33311E-17

C_21

VDD#1

A#1

1.32804E-17

C_22

VSS#1

Y#1

3.39784E-17

C_23

Y#2

VDD#1

3.77889E-17

C_24

VDD#1

A#4

5.22662E-17

C_25

Y#2

A#4

9.12325E-17

C_26

Y#1

A#7

6.11434E-17

C_27

A#7

VSS

3.31047E-17

C_28

VSS#1

A#7

5.13338E-17

C_29

VSS

0

4.01639E-20

C_30

VSS#1

0

8.33704E-20

C_31

VDD#1

0

8.33704E-20

C_32

Y#2

0

4.01639E-20

*

*

.ENDS INVX1

.config文件

set model_file /home/peter/LibraryFile/smic13/models/hspice/cis013_ll_fsi_v1p0.mdl

set model_file /home/peter/LibraryFile/smic13/models/hspice/cis013_ll_fsi_v1p0_nmoscap.ckt

set model_file /home/peter/LibraryFile/smic13/models/hspice/cis013_ll_fsi_v1p0_res.ckt

set netlist_suffix .sp

set template_suffix .opt

set netlist_dir ./source

set simulator_exec /opt/synopsys/HSPICE_2015_06/hspice/bin/hspice64

set input_template_dir ./Template

set output_library ./Output/smic13_tt.lib

set work_dir work

set farm_type nofarm

set templates false

set timing true

set power true

set nldm true

set nlpm true

set design_rules true

set ccs_timing true

set ccs_power true

set log_file ncx.log

朋友我最近也在学习用ncx的用法,能否请教个问题。是这个input_library怎么生成的,你有没有教程啊,可以分享下么。谢谢你了

我就在这个论坛是找的教程