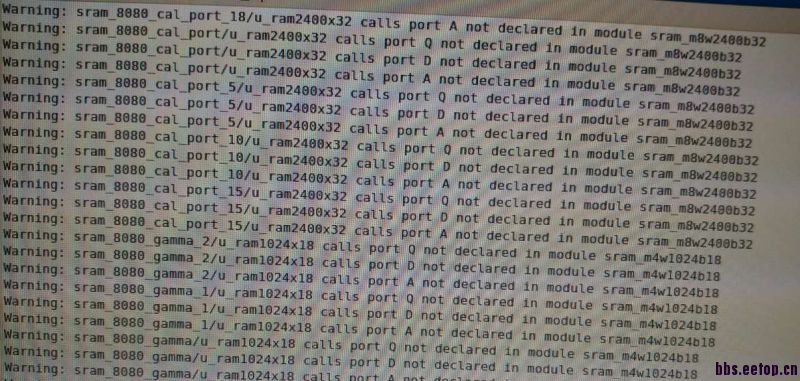

v2lvs过程报出的warning,Calibre lvs因为这些warning运行不下去

Encounter输出.v文件,然后运行v2lvs,在转换成spice网表的过程中报出了"port not declared in module"的warning,不清楚是什么原因,求助大侠解疑.

求共同解决!

http://bbs.eetop.cn/thread-554850-1-1.html

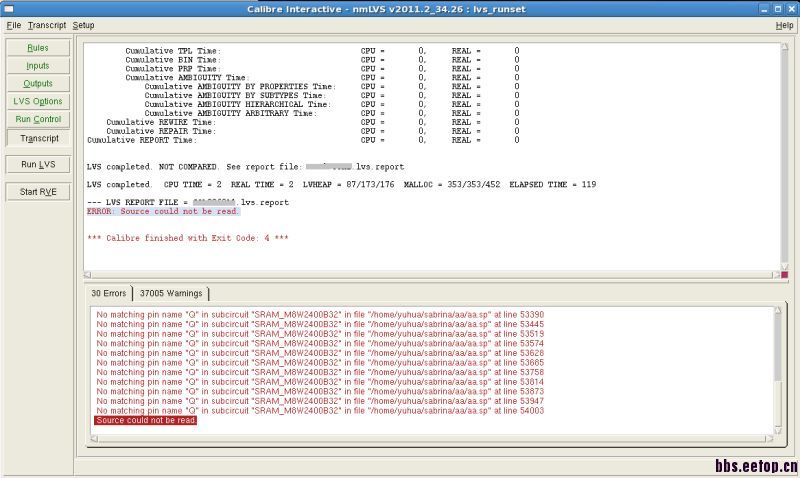

这些都是warning,不会因为这些跑不下去,去看看error

好像看起来是跑不下去的

你转spice的命令是啥

v2lvs的warning通常可以无视, 只要能完成就行,不会影响到error的,

查查别的原因

贴图很不清楚,

簡單說就是你的netlist與spice不符,可能你sram module有150個pin

但你include的sram.spi 的pin的數量不match

於是對不起來.

看上去用的不咋对。你查过v2lvs的具体用法了么给你个简单的例子:

v2lvs -o output.cdl \

-l ref.v \

-s ref.cdl \

-v input.v \

-s0VSS -s1 VDD

你好,我也感觉是我转化的spi文件跟include的sram.cdl文件的网表端口名不一致,不知道为什么会出现这种情况,请问该如何解决呢?

嗯,谢谢小编的解答,好像找到了点头绪.

提供你一個debug的方式,舉圖片中的例子來說,

sramaaa/ccc call port A not declared in module ddd

依照這行敘述,

我預估你可以在icc的output verilog netlist裡,

找到 sramaaa/ccc這個cell, 然後ref_master_cell是 ddd

但是在你的ref cdl裡面

defined的 .subckt ddd

裡頭的pin list 沒有A這個pin

先確定狀況是這樣的,

然後去找提供你這個sram data的vendor要

要嘛是.lib define有問題

要嘛是cdl有問題

不過一般是用sram compiler 出來的

不太應該出現這種錯誤

請vendor幫你double check囉

我也碰到这个问题 查了一下v2lvs的工作选项 用-lsr sram.cdl 就能解决bus不匹配的问题。搞了大半天找错误和解决方法。

Thanks for your share.