求助:初学soc encounter,请问给位大侠怎样将digital布成自己所需要的形状啊?

初学soc encounter,请问怎样将digital布成自己所需要的形状啊?

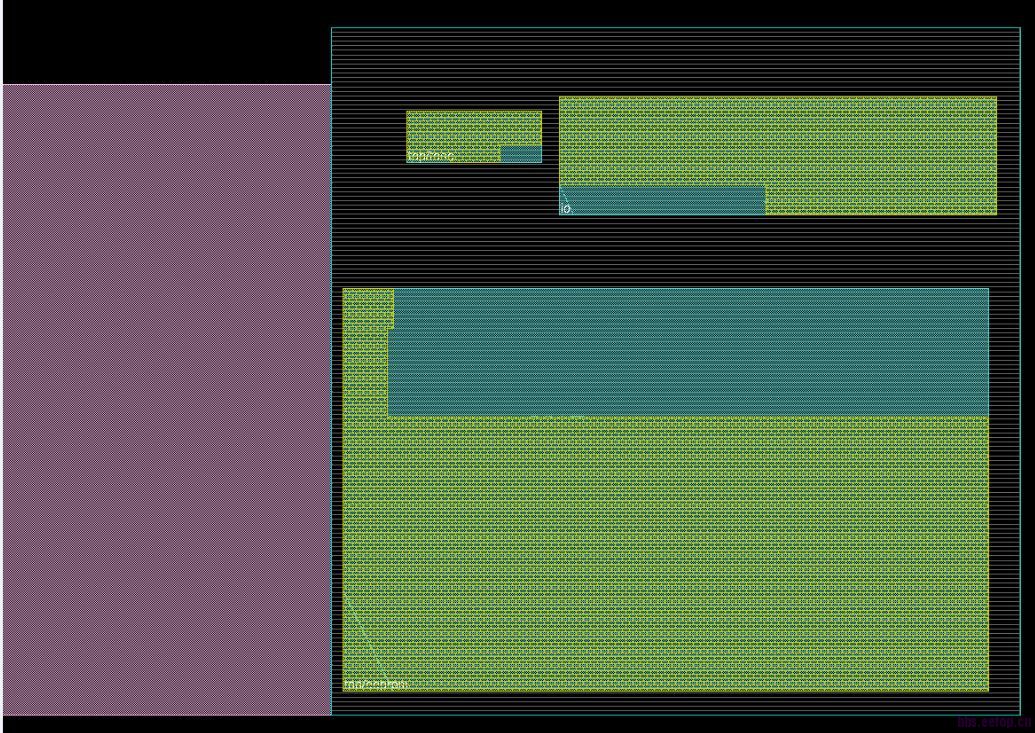

如图:

现在的情况是:只有整个电路的.v文件,包括图中的block1,block2,block3,digital。没有单独的digital的.v文件。

目前的做法是:用整个电路的.v文件,以及图中的block1,block2,block3的.lef文件,来做自动布局布线,做出数字版图希望得到上图中的形状和摆放?整个top图需要如上图所示?

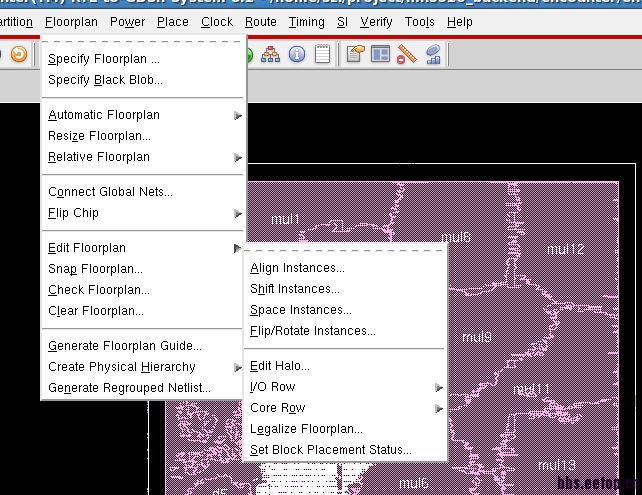

是不是要在Floorplan——》Edit Floorplan下的选项中操作一下啊?

谢谢!

block1,block2,block3是hard Macro?

其实也很简单的,按照size设定好,然后按照位置摆放,别忘了加个halo,对齐的话,可以采用relative Floorplan的功能

digital的那块可以改变module的形状得到。

可能我表达有错误,block1,block2,block3不是自动布局布线中的block,它们是电路中的子电路:eeprom,osc,和IO模块,因为现在只有整个电路的.v文件,没有单独digital的.v文件,所以是用top .v文件和eeprom,osc,和IO模块的.lef文件来做自动布局布线,希望得到下面的布局:

但是,我现在调用的top .v文件和eeprom,osc,和IO模块的.lef文件,design——》Design Import后,然后手工移动,得到的是下面的图形:

我们osc,和IO模块的.lef中规定osc,和IO模块的形状是“L”形。可现在得到的都是矩形。与别人第一版做的不一样,见图一,是“L”形。

是不是要reshape一下现在得到的osc,和IO模块的矩形?还是,我们需要设置一下.lef文件,或者调用时设置相关选项。

我们最终想得到下面的top图:

谢谢!

OSC eeprom IO只是借用lef信息的macro对吧?

只有digital部分是stdcell组成的,对吧?

如果是,那osc,和IO模块的形状是不是L形状,是由具体layout信息决定的呀,如果版图中他就是个方的,那macro的lef是真实的话,改了也不对呀。你只能那么用它

你可以随便做一遍,最后merge gds后出来一个版图看看,那样你就懂了。

那这你们这个LEF文件产生的又问题吧. 虽然LEF的MACRO只能定义成RECT,但是可以用OVERLAP层来指定其中哪些区域是实际上占用的,剩下的区域还是可以给top的std cell用

谢谢啦!

路过,学习~

你好,对于lef出来的东西,应该不能直接reshape

你说的digital.v是什么意思?是一个空的module?我记得edi有个specify blackblobs的功能,但是没用过,不知道。如果digital.v是一个stdcell组成的module,那可以在floorplan的时候relativeFPlan命令弄进去,然后还可以reshape等。

lu guo xue xi

想问下如何利用这个 Edit plan呢

我想用一下 shift Instances 可是每次都会提示:

**WARN: (SOCSYT-3130):Please select at least 1 instance/module to shift.

想问下,这个是怎么回事?如何按照小编您说的 按照指定位置摆放module呢

还有个小问题,小编知道在哪里设置 max density吗 是在sdc文件中吗

我用的是 SOC encounter8.1

多谢啦

encounter有三个视图,你到floorplan里面试试呢

max density,在place的时候设置

还是同样的错误啊 怎么一直提示我要先选中一个instance呢,怎么选中呢还有设置max density使用脚本吗 用gui的话 在place的哪里设置 没有找到啊

在floorplan中 一直是自动布图的 怎么才能自己放置每个模块的位置呢 直接手拖吗

路过学习