28nm后端DRC问题,在Via上面有很多edge length引起的min area问题

时间:10-02

整理:3721RD

点击:

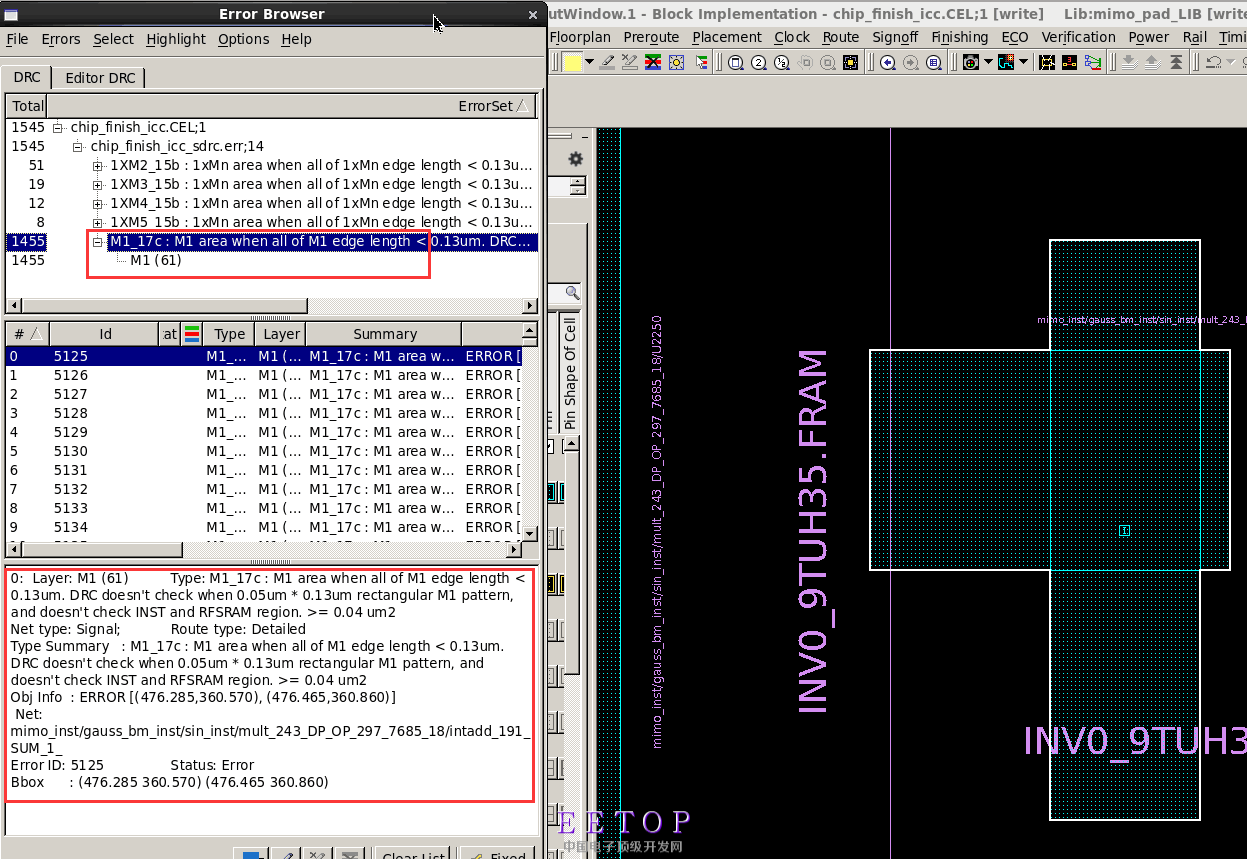

如题,基于28 nm工艺,我在ICC里面PR之后,检查布线DRC不存在违反,到Calibre里面检查有很多这种edge length引起的min area的问题,数目非常多,应该是无法手工修复的。

我现在想用ICV来解决这种问题,发现也是水平有限,能修复的很少,请问一下,这种问题在后端中该如何解决呢?谢谢各位大牛了

DRC如下:

Layer: M1 (61)Type: M1_17c : M1 area when all of M1 edge length < 0.13um. DRC doesn't check when 0.05um * 0.13um rectangular M1 pattern, and doesn't check INST and RFSRAM region. >= 0.04 um2

分析之后,发现基本上都是在M1引出Pin的地方插入的Via和Pin形状拼在一起之后就形成了多边形,由于Via的M1尺寸小于0.13,所以引起了MinArea这个规则的检查。

此外在M2 M3 M4 M5等上面都有这些类似的问题

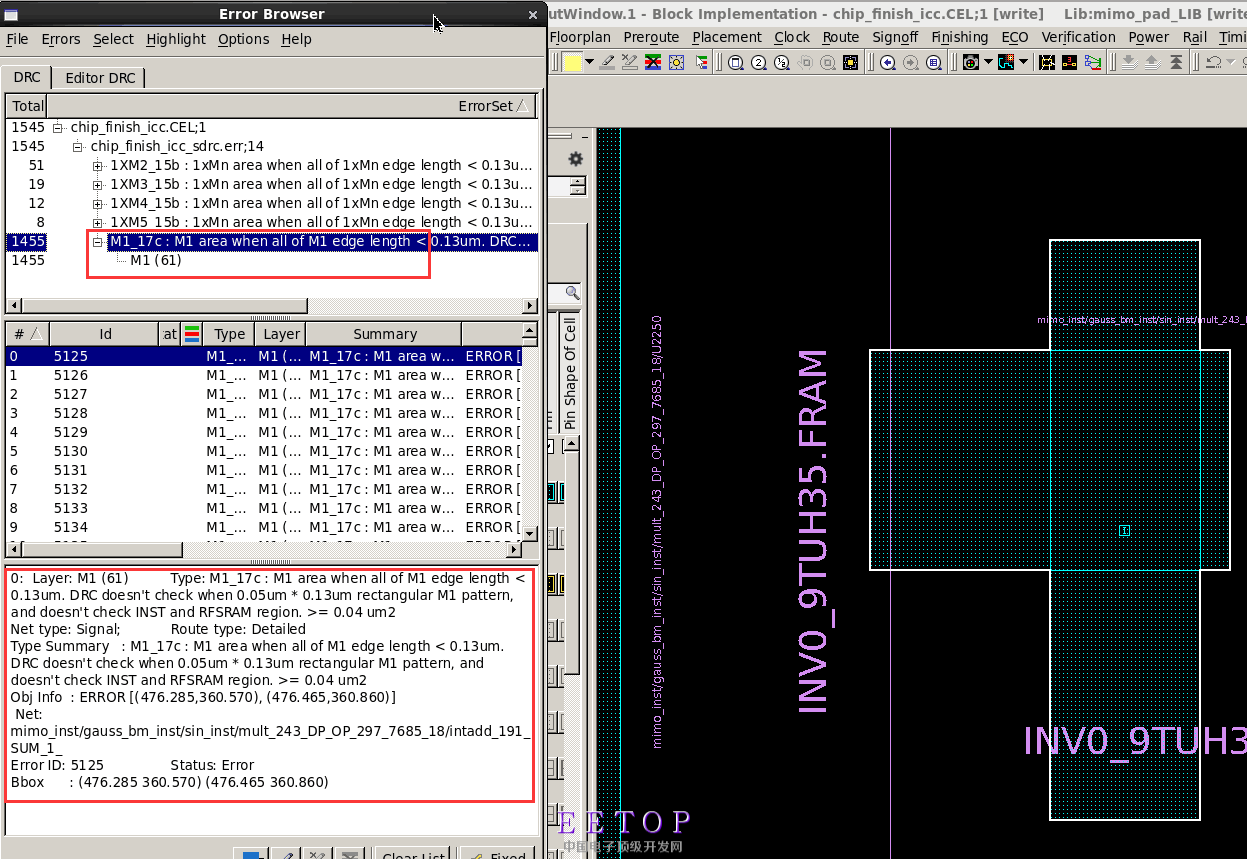

如上图所示,一层Via上面是另一层Via,因为一个是横着放的,所以另一个是竖着放置的,他们交叉之后又会引出上面同样的问题,哎,这个问题该如何解决呢?

请各位后端大牛帮帮忙,谢谢了

我现在想用ICV来解决这种问题,发现也是水平有限,能修复的很少,请问一下,这种问题在后端中该如何解决呢?谢谢各位大牛了

DRC如下:

Layer: M1 (61)Type: M1_17c : M1 area when all of M1 edge length < 0.13um. DRC doesn't check when 0.05um * 0.13um rectangular M1 pattern, and doesn't check INST and RFSRAM region. >= 0.04 um2

分析之后,发现基本上都是在M1引出Pin的地方插入的Via和Pin形状拼在一起之后就形成了多边形,由于Via的M1尺寸小于0.13,所以引起了MinArea这个规则的检查。

此外在M2 M3 M4 M5等上面都有这些类似的问题

如上图所示,一层Via上面是另一层Via,因为一个是横着放的,所以另一个是竖着放置的,他们交叉之后又会引出上面同样的问题,哎,这个问题该如何解决呢?

请各位后端大牛帮帮忙,谢谢了

interesting, I thought the rule already defined the minimum area rule, why it still generate the violations

设置打via只能打在M1里

smic的比较恶心,只要有十字交叉的形状都会有最小面积的问题,更新一下RULE说不定就没了。他都说了不检查某种特定的形状,也许是语法bug导致的ignore失效。已经一年多没做了不知道现在什么情况了,去年用的内部最新RULE就不会报出来了。

您好,非常感谢您的回复,请问一下,在ICC里面如何设置只在M1里面打Via呢?谢谢您了

哦哦,好的,非常感谢您的回复,那我问一下他们内部,看能否获得最新的DRC文件吧,谢谢您了