后端面试--每日一题(018)

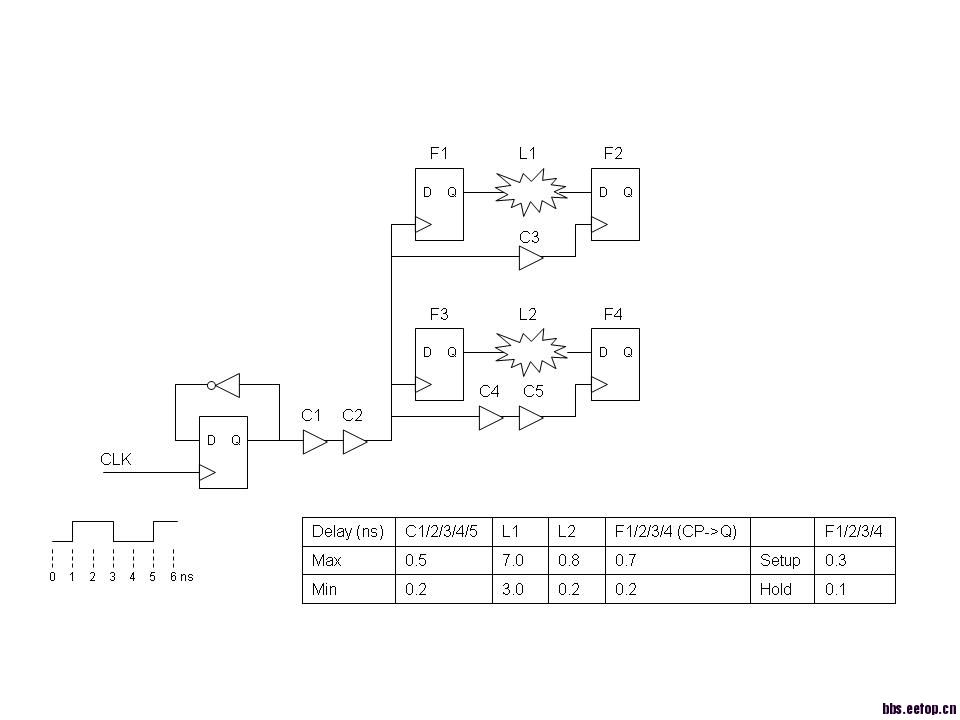

using the same logic as question #17, considering OCV on clock path only, which clock buffer will be used for OCV derating calculation and which clock buffer will not (a.k.a. CPPR)?

如果考虑clock path的OCV,在第17题的电路里面,哪几个时钟BUF要被用来计算OCV的derating,哪几个不用(又叫CPPR)?暂不考虑X-talk产生的incremental delay

难度:2

总是搞混,cppr 与ocv区别是什么啊,我感觉derate 是与cppr相关的,

是不是考虑net 的derate和cell 的derate就是ocv ,只考虑cell的derate就是cppr啊,

derating是什么呀,我一直以为ocv就是在data path和clock path,对setup采用max,min,对hold采用min,max呢,希望从这个题上可以理解到

ocv和derate是两回事吧。可以ocv兼带derate。也可以两者单独用。

“ocv就是在data path和clock path,对setup采用max,min,对hold采用min,max呢”这个应该没错。

derate相当于人为调整系数。 譬如把data path的*1,clock path*0.9保持不变来算setup。 data path *1,clock path * 1.1来算 hold。 我看到的资料一般这么算,但我想,data path * 1.1,clock path*1来算setup,data path *0.9, clock path *1算hold 应该也一样道理

没看清题目,应该是c1,c2不算。c3,c4,c5要算

C1 C2不用算入derating(应该是也计算过,但是会通过CRPR弥补),C3,C4,C5 要计算derating

#5和#6正确

以下是几个概念的通俗解释。如果谁想翻出书上的定义来较真,我闪。

OCV:因为制造工艺的限制,同一芯片上不同位置的单元会有一点差异,这就是OCV。现在还有LOCV和AOCV,暂且不提。

derating:是计算OCV的一种简单方法,在某个单一条件下,比如WC或者BC,把指定path的延迟放大或者缩小一点,这个比率就是derating。注意,这里要强调的是某个单一条件,要么是WC,要么是BC,不能把WC和BC混在一起,再OCV,因为那样太悲观,实际上是很难发生的。

除了derating以外,在使用incremental SDF的时候,也会对OCV发生作用。这是明天的问题,比较有难度。

CPPR:一条path的start flop和end flop的时钟路径,有时会有一部分是重合的,重合的部分不应该算OCV(注意,这里假设没有使用incremental SDF),这就叫CPPR。

那么也就是ocv比cppr更悲观了吧

再请教一下,你说的放大和缩小,两个data path和clock path都要同时的吗,那这样的话,其实就是在已有的slack上乘以那个deration就是了,不知道我说的对不对

CPPR是OCV计算中的一部分

一般不需要在clock和data path上同时都做derate

那是在哪条路径下做deration呢?data 还是clock呀,我猜setup就是clock上做,hold就是在data上做

这个没有统一的标准,依照reference flow的建议做,加在clock path上的比较多。

汗,是crpr。大家不要一个疏忽了剩下的都跟着好不。

汗,是crpr。大家不要一个疏忽了剩下的都跟着好不。

Cadence 叫 CPPR: Clock Path Pessimism Removal

Synopsys 叫 CRPR: Clock Reconvergence Pessimism Removal

都是一个意思啦!

是俺见识不够啦,嘿嘿

今儿上线晚,看到题目时候答案都出来了。

有错就改,好童鞋!

一旦得到第一个正确答案,就会马上确认。剩下的就是借题发挥的深入讨论了

嗯,关于OCV,陈老大说的只在单独一个corner,WC或者BC下考虑,而不是BC_WC混着来,这点的确是很多人都会忽略的,我也曾经有过这样的误解,似乎还拿自己的错误答案给人解答过。

那就是说在ocv计算中可以有cppr或没有cppr,没有的话更悲观,有cppr的话乐观一点。

没有cppr是不现实的过度悲观,或者叫“跟自己过不去”

拿你的解答去面试,挂了的话,人家不找你玩儿命,嘿嘿

那那个derate的系数怎么针对项目的设计和工艺情况进行计算得出呢?

提问的有点小白^_^不过确实想知道

derate系数感觉都是经验值啊。 自己留个裕量。

另外一个考虑X-talk引起的clock path delay不一致,在会不会作为CRPR一部分考虑?为什么?

那BC_WC模式下是混着来的吗? 计算hold用min,计算setup用max?

xuexixuexi

有人能解答一下x-talk是什么分析吗,还有enable si,小白问题