icc timing计算问题

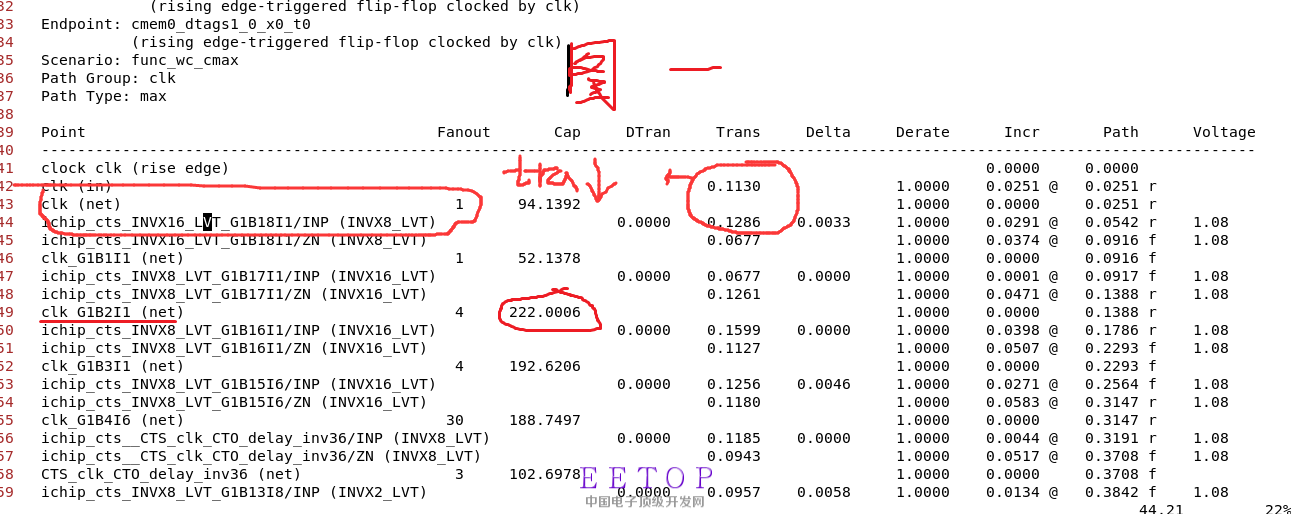

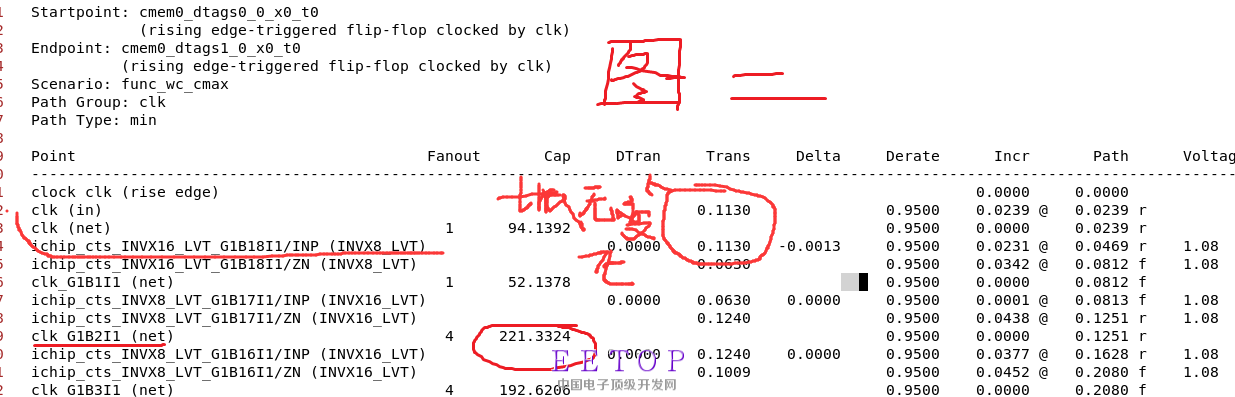

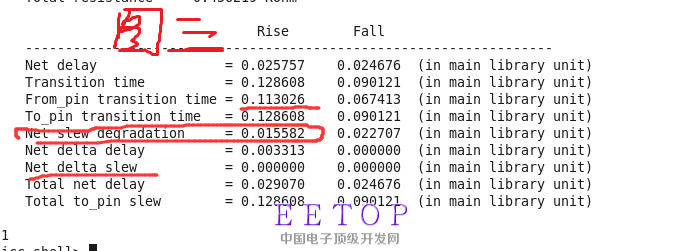

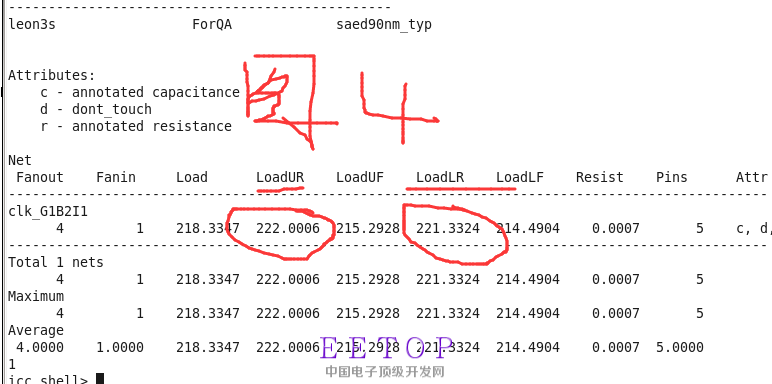

大家好,小弟最近route后考虑cross talk,报timing时候发现一个问题,如下图图1,所示为爆出来的一个reg reg path的setup,发现clock端口到第一个invert有个transtion的变化,从0.1130降到0.1286;接着在图2上爆出同样的path,hold的报告,transition无变化,都是0.1130.,然后通过report delay cal爆出发现图三里有个net slew degradation,net delta slew,不知这个是什么?net slew degra是不是指的电阻效应?这是第一个问题;接着第二个问题,图一的clk_GIB2I1 net上的爆出cap是222.0006,而图二hold的这个net的cap是221.3324,这个区别从哪来的?通过report net爆出来,见图四,这两个值分别对应图四的loadUR和loadLR,查找一些userguide没找到,希望知道的人,告知下,谢谢大家。

up。

没人知道吗?求教大神、

help.....

看得真仔细!

LoadUR估计是Load Upper Rise吧 (LR, Lower Rise).

library里描述pin capacitance可能是一个range(for min/max ect.)而不是一个固定的值

谢谢r兄的回复,library里确实有个range范围,之前关注过,懂了,那图1,2里的net slew degra是怎么回事呢?是wire电阻引起的吗?为什么min没有?还有那个net delata slew是跟cross talk有关的吗?我看很多都是0,也就是串扰对transition的影响不计入了,谢谢回答。

第二个问题关于setep和hold报出cap的值有差异,个人理解是因为ocv的原因。

不是哦,ocv的设置只会对delay进行derate,不会影响报的cap...

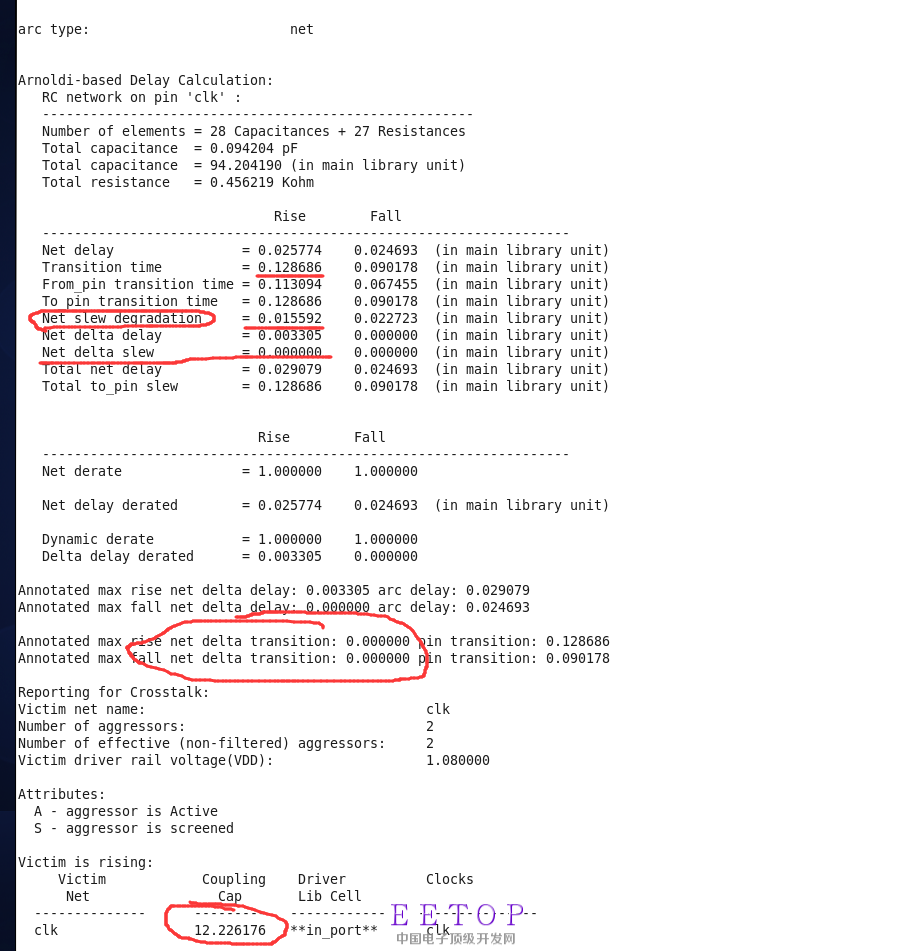

图3中的net slew degra与net delta slew是怎么来的?请教知道的兄弟不吝赐教。

up...

第一个图里面transition的变化,应该是输入端的transition换到输出端的。所以有transition变化。

但是第二个图里面的transition在输入和输出端居然没有变化,是不是因为刚好算出来的输出端transition是同样的值。

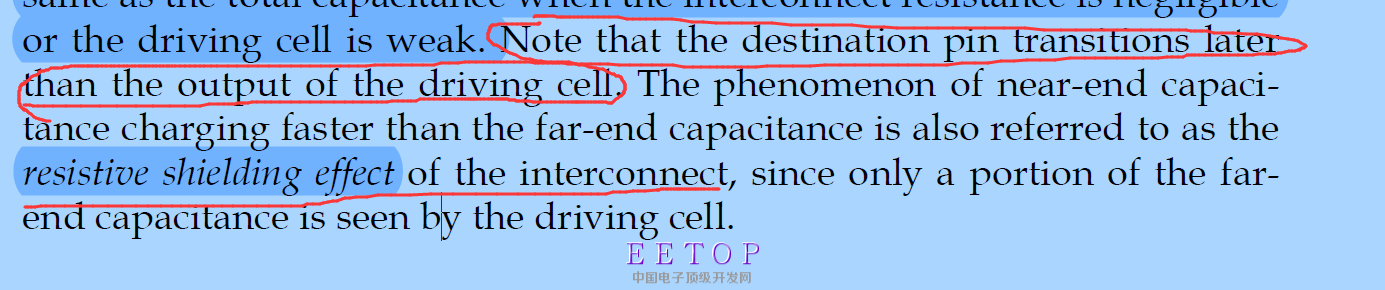

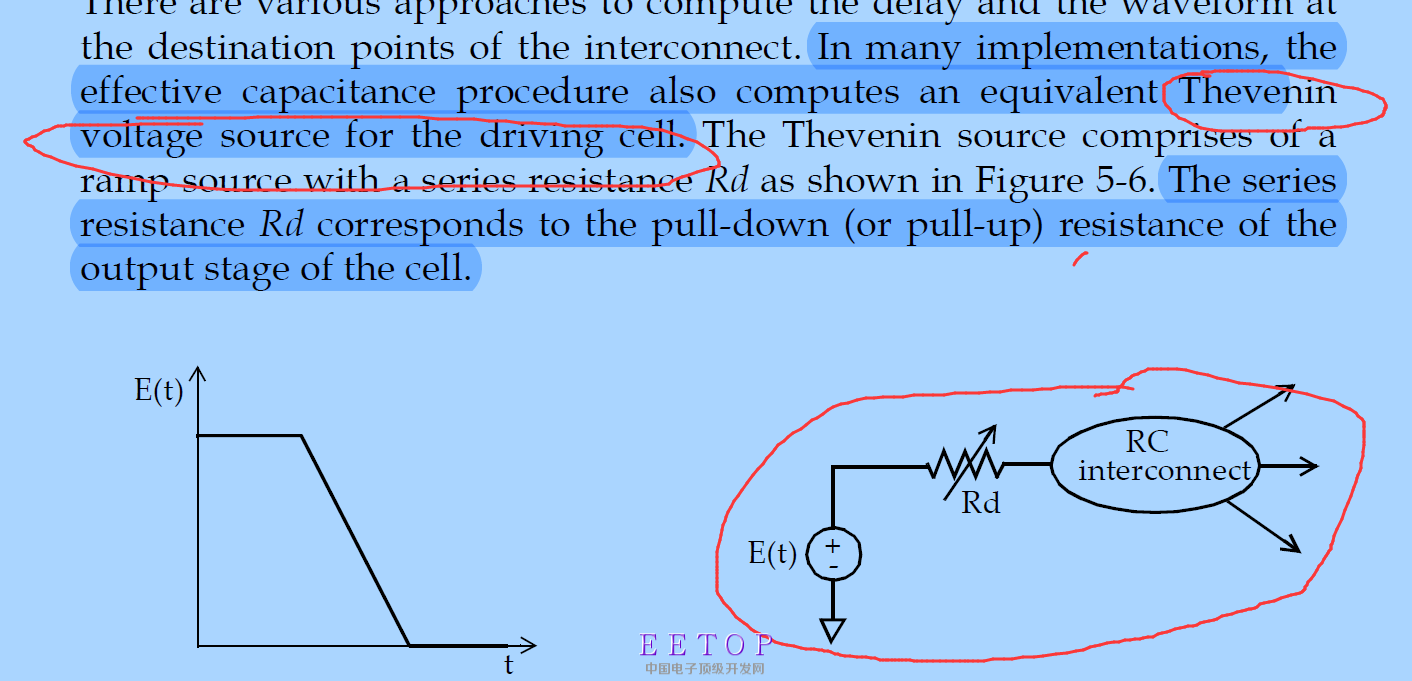

谢谢A兄的回答,sta的文档说,driving cell的输出pin的transition到destination pin的transition会延迟,因为互联电阻的原因,见下图,destination pintransition的计算是通过戴维南电压源来计算的,同样见下图,不知道我理解的对不对,既然互联有电阻,net slew deg是不是互联电阻的原因,那为什么同样一个互联线,min情况下就不一样了呢,operating condition max和min都是一样的,可参考帖子图1,谢谢回答。

需要高手解决啊!最近两年都没看到陈小编都没出现了。

up....

min和max的电阻和电容应该是根据min和max两个路径的情况来算的吧?所以大概是说,A-B是MAX路径,还有一条C-B是min路径?这里的min和max我理解为的是时序上的min和max两个。

谢谢回答,min和max指的是start-end间算出的最大路径,然后我图里的max,min前面都是同样的path,当然min和max算法不一样,现在问题是这个net slew是从哪来的,为什么min没有.

up...

Driving 不一样,tlu+不一样,对min 下report delay cal看看。估计是net cap在一定的范围net slew可以忽略,可以通过不断增加fanout或者调整net length做实验

谢谢回答,pvt,tluplus设置的max,min是相同的,report delay cal也报出来了,并没有显示net slew的计算,而且报出的max和min是同一路径,现在是不清楚算法的计算方式,至于您说的设置pvt,tlup不一样,可以尝试看看效果,而现在的情况就不清楚了,如果真的是cap比较小,但max和min的cap是相同的哈,为什么会不一样呢,谢谢。

max和min的transition不同,我的理解是max / min 的 timing window 不一样,crosstalk的影响不同, 导致transition time 有差异。(report_delay_calculation应该有option可以报出crosstalk的情况)要么再查一下clk这个port上113ps 的transition是怎么来的?(set_input_transition/set_clock_transition还是set_driving_cell来的?)

谢谢回答,我并没有设置timing window,当然工具会按最差情况叠加cross talk影响,crosstalk计算的都是deta delay吧,如果真影响transition的话我觉得也是以下图那个net delta slew的形式表现的吧(sta书籍里都是提起positive delay 和negative delay,transition没提),我用report delay cal爆出过cross talk,里面只写了coupling cap值大小,重新报的见下图:

别沉。

感觉是max和min下的load不一样导致的

为什么没有人来解决这个问题呢?很有意义的问题,请问小编这个问题现在知道答案了吗?可以讲一下吗

thanks for the info