decap filler一定要加? 何时加? 加何处? 加多少? 能完全替代std filler?

对,一定要加, route之前加, 空的地方加, 尽量多加,一般不能完全取代普通filler,

因为decap filler一般做的比较大, 而且有metal1 的地方 都不能加, 会有drc error、short

谢谢小编。 一个疑问: route过程中也会有opt吧,如果也有cell的move甚至size,过早填充这么多decap filler是不是会影响routing的opt呢?

哈哈,和我问的问题一样啊

http://bbs.eetop.cn/thread-316772-1-2.html

再请教一下小编,为什么是rout之前加,不在完成所有版图之后再加呢?

要是rout之前就填满了decap,rout之后发现timing什么的不满足,要insert buffer/upsize cell进行优化,岂不会没空间了?

decap填充,对设计会不会有其他影响?比如timing和power?

还有,有metel 1的地方填充decap为什么会导致DRC和short呢?

metel 1不是到处都是么?std cell的电源地就是metel 1了,那还怎么添加?

decap cell 里面通常有很多metal 1 , 如果route之后加,很多已经有的 metal 1 routing 会使得加的比例大大降低,

route之前加,只是给router一个信号:就是尽量少在decap的地方用metal 1 routing,这个对于decap的比例是有很大好处的,

即使后面route_opt 要优化,去掉decap filler再重新添加,也能维持这个router 的 patten趋势,

这样可以使得加的decap 增加啊

你们可以做个试验:

分别route_opt 之前和之后加, 然后都做优化,看看最后的decap filler谁多

一般都是route_zrt_auto 先route完 ,存个cell, 然后去掉filler, 再开始route_opt ,

明白了

我们是route 全部结束,或者说physical 部分,包括修hold插buffer结束后才 add cap filler ,加完之后再 add fiiler (no matal1) .

icfbicfb 小编说的,我觉得会影响到routing resource但对于 cap filler 的比例肯定有很大改进

后端很多都是一种trade off, power size timing 等

如果size 很紧张,routing很紧(我们就是这样 )所以采用先保证route 能通过,所以后插 cap filler,毕竟里面有metal1,会影响到一些横向的绕线

楼上的兄弟, 你这种做法有没有实验看看decap cell insert后有没有影响到timing,真是break到route?

sta 影响比较小,但是 si 的影响肯定有的

不过这个没关系,我们本来就是 加完 cap filler 和 filler 以及 dummy fill 之后 的spef 来 跑 ptsi 啊

至于是否会影响到route,我没有实验过,只是理论估计 track 就那么多,cap fill 占用了,其他std cell 和 shape 就没有track了,这个影响主要是metal 1 和metal2 的

就像前面说的,这是trade off,不是说我的做法就好只是我们用的是这个flow,即所有的timing都clear以后再加这些cell

举个例子 : 有1000个buffer 插入 用来修hold,如果 已经加入filler (cap filler ),那我只能将buffer放在远一点的位置,当然如果cell空不在此例中,这样最直接的影响就是我(或者工具)不得不将cell 放到较远的地方,这样可能会产生更长的连线 进而产生 si 以及 setup的问题

现在看ICC的userguide,也是在route之后加,route之前加效果一般~

请问下小编大人,

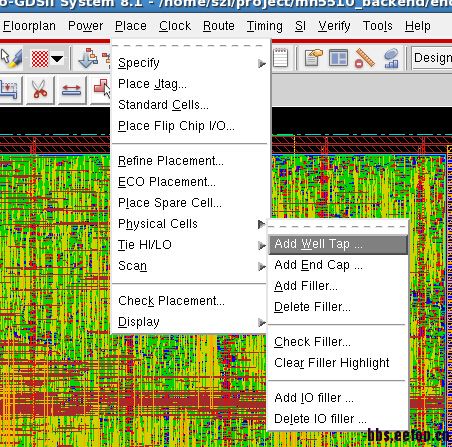

这个decap 是指的这里面的吗?是哪个

学习了!

小编,问个小概念问题! filler cell有两种,一种是含metal的,一种是不含有metal;这里面含有metal的filler和decap cell是同一个吗

先多谢啦!

就是这个well tap cell

filler cell有两种,一种是含metal的,一种是不含有metal;含有metal的是Decap,不含metal的就是简单的Core filler

现在我们学的也是先route再加filler,看了整个讨论也是学到很多