利用cadence进行后仿时遇到的问题

时间:10-02

整理:3721RD

点击:

各位大神好 小弟在用cadence进行后仿的时候 对测试文件进行了view config,可以对schematic view和calibre view进行切换仿真 奇怪的是 对于同一个测试电路 它的schematic view仿真输出结果正确 而calibre view却输出错误结果 而我的版图已经通过了DRC和LVS检测 百思不得其解 还请诸位前辈指正

检查两点:1. calibre提取时,寄生电阻电容没有选择array,导致部分电路短路。

2. symbol的pin脚跟layout的pin没有对上,最好是重新生成symbol。

遇到这种情况,最好检查网表文件

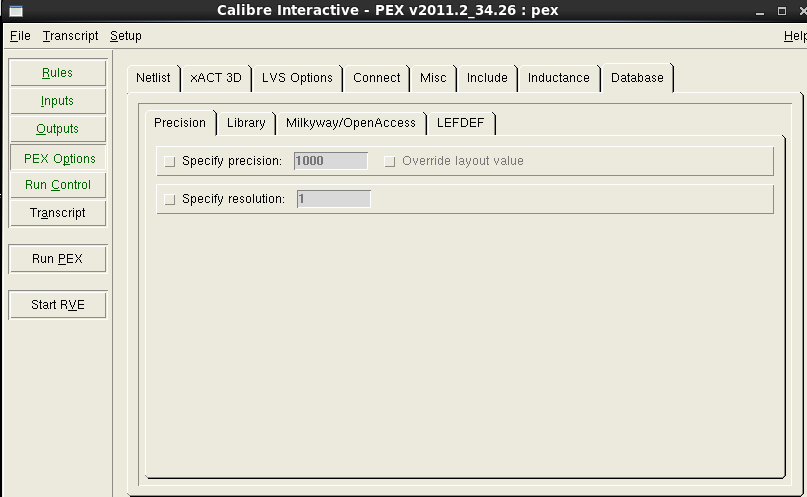

请问您说的生成calibre时没有选择电阻电容array是什么意思?是下图中我标注的地方吗?

不是,应该在PEX options里面吧,因为你采用了calibre view,仿真生成的网表是由schematic生成,而不选择这个选项,有可能出现两个节点由于位置太靠近,造成短路。当然这是我之前做项目时遇到的现象,不知道你是否是遇到同样问题。

还是没找到 那个选项在哪儿 跪求大神指教。

2楼给的怀疑是对的。但array不是在pex option,是在pex跑完之后提取calibreview的界面找吧---

使用calibre view的时候跳出来的那个里面设置,不在calibre的pex option里面设置,而且用calibre cell.map的时候 ,反标回去到calibre view里面的期间属性也要debug,反标出来的器件property也可能是错误的,最好先用pex 网表跑下仿真确认结果

出现同样问题,DRC和LVS全部通过,提参的时候报错很多shorted。

arrayed以后完美解决。

总结下来应该就是schematic模式下,放置的过近导致了错误连接。