求各位大神解决下calibre中一个奇特的LVS问题(LVS OPTION电位设定方面的)

时间:10-02

整理:3721RD

点击:

这几天画了一个版图,结果跑LVS总是出现如下图的错误

图中的ERC错误是因为所画的有些器件的B极不是连接到GLOBAL电位的,而是连到一个器件的输出端。

验证分析的结果是calibre会把版图上的OUT1_B这条net认成OUT0_B,还有就是认不出INB这条net。

然后从上图中可以看到有20个错误,但如果我把版图左右翻转、上下翻转或者90度翻转,错误的个数会改变,变成23、26、27或者28个错误。

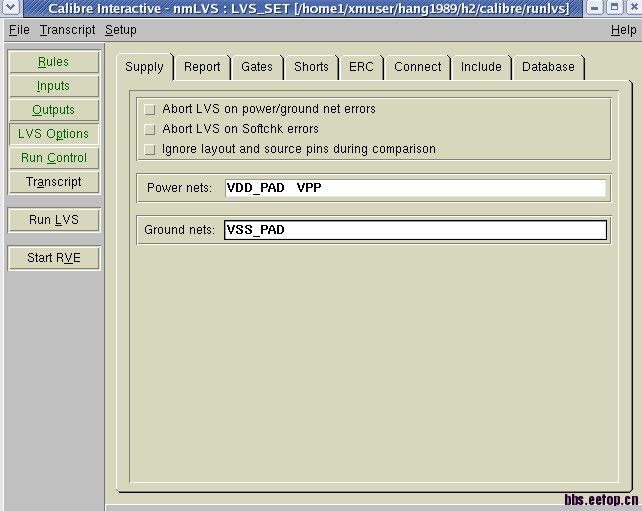

如果我按照下图在LVS OPTION中设定好它的电位,结果就是下下张图中显示的——错误没有了。

求各位大神指教这是怎么回事,还有就是这张版图能直接这样投入使用不,还是说需要改正?(试着改了几天了,就是解决不了这问题啊 ,求有懂这问题,或者遇到过并解决掉这种问题的达人帮忙啊,谢谢!)

以下附上LVS report(是跑LVS出现20个错误时的report)

##################################################

####

##C A L I B R ES Y S T E M##

####

##L V SR E P O R T##

####

##################################################

REPORT FILE NAME:delay_pp07.lvs.report

LAYOUT NAME:/home1/xmuser/hang1989/h2/calibre/runlvs/delay_pp07.sp ('delay_pp07')

SOURCE NAME:_source.net_ ('delay_pp07')

RULE FILE:/home1/xmuser/hang1989/h2/calibre/runlvs/_G-DF-EFLASH_EE2PROM162N-1.8V_3.3V-2P6M-HV_R-CALIBRE-LVS-0.1_P1_01.txt_

RULE FILE TITLE:162nm Embedded Flash and Embedded E2PROM 1.8 V/3.3 V 2P6M High Voltage Reduction Process

CREATION TIME:Thu Jan 17 09:38:15 2013

CURRENT DIRECTORY:/home1/xmuser/hang1989/h2/calibre/runlvs

USER NAME:hang1989

CALIBRE VERSION:v2008.1_32.21Tue Apr 1 22:33:09 PDT 2008

OVERALL COMPARISON RESULTS

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Different numbers of instances.

Error:Connectivity errors.

**************************************************************************************************************

CELLSUMMARY

**************************************************************************************************************

ResultLayoutSource

------------------------------------

INCORRECTdelay_pp07delay_pp07

**************************************************************************************************************

LVS PARAMETERS

**************************************************************************************************************

o LVS Setup:

// LVS COMPONENT TYPE PROPERTY

// LVS COMPONENT SUBTYPE PROPERTY

// LVS PIN NAME PROPERTY

LVS POWER NAME"?VCC?" "?VDD?" "?VCC?" "VCC:?"

LVS GROUND NAME"?GND?" "?VSS?" "?GND?"

LVS CELL SUPPLYNO

LVS RECOGNIZE GATESALL

LVS IGNORE PORTSNO

LVS CHECK PORT NAMESYES

LVS IGNORE TRIVIAL NAMED PORTSNO

LVS BUILTIN DEVICE PIN SWAPYES

LVS ALL CAPACITOR PINS SWAPPABLENO

LVS DISCARD PINS BY DEVICENO

LVS SOFT SUBSTRATE PINSNO

LVS INJECT LOGICNO

LVS EXPAND UNBALANCED CELLSYES

LVS EXPAND SEED PROMOTIONSNO

LVS PRESERVE PARAMETERIZED CELLSNO

LVS GLOBALS ARE PORTSYES

LVS REVERSE WLNO

LVS SPICE PREFER PINSNO

LVS SPICE SLASH IS SPACEYES

LVS SPICE ALLOW FLOATING PINSYES

// LVS SPICE ALLOW INLINE PARAMETERS

LVS SPICE ALLOW UNQUOTED STRINGSNO

LVS SPICE CONDITIONAL LDDNO

LVS SPICE CULL PRIMITIVE SUBCIRCUITSNO

LVS SPICE IMPLIED MOS AREANO

// LVS SPICE MULTIPLIER NAME

LVS SPICE OVERRIDE GLOBALSNO

LVS SPICE REDEFINE PARAMNO

LVS SPICE REPLICATE DEVICESNO

LVS SPICE STRICT WLNO

// LVS SPICE OPTION

LVS STRICT SUBTYPESNO

LAYOUT CASENO

SOURCE CASENO

LVS COMPARE CASENO

LVS DOWNCASE DEVICENO

LVS REPORT MAXIMUM50

LVS PROPERTY RESOLUTION MAXIMUM32

// LVS SIGNATURE MAXIMUM

// LVS FILTER UNUSED OPTION

// LVS REPORT OPTION

LVS REPORT UNITSYES

// LVS NON USER NAME PORT

// LVS NON USER NAME NET

// LVS NON USER NAME INSTANCE

// Reduction

LVS REDUCE SERIES MOSNO

LVS REDUCE PARALLEL MOSYES

LVS REDUCE SEMI SERIES MOSNO

LVS REDUCE SPLIT GATESYES

LVS REDUCE PARALLEL BIPOLARYES

LVS REDUCE SERIES CAPACITORSYES

LVS REDUCE PARALLEL CAPACITORSYES

LVS REDUCE SERIES RESISTORSYES

LVS REDUCE PARALLEL RESISTORSYES

LVS REDUCE PARALLEL DIODESYES

LVS REDUCEC(NCAP_18_G2_EF_UCFN)PARALLEL NO

LVS REDUCTION PRIORITYPARALLEL

// Trace Property

TRACE PROPERTYmn(n_18_g2_ef_ucfn)l l 3

TRACE PROPERTYmn(n_18_g2_ef_ucfn)w w 3

TRACE PROPERTYmp(p_18_g2_ef_ucfn)l l 3

TRACE PROPERTYmp(p_18_g2_ef_ucfn)w w 3

TRACE PROPERTYmn(n_33_g2_ef_ucfn)l l 3

TRACE PROPERTYmn(n_33_g2_ef_ucfn)w w 3

TRACE PROPERTYmp(p_33_g2_ef_ucfn)l l 3

TRACE PROPERTYmp(p_33_g2_ef_ucfn)w w 3

TRACE PROPERTYmn(n_pg32_g2)l l 3

TRACE PROPERTYmn(n_pg32_g2)w w 3

TRACE PROPERTYmn(n_pd32_g2)l l 3

TRACE PROPERTYmn(n_pd32_g2)w w 3

TRACE PROPERTYmp(p_l32_g2)l l 3

TRACE PROPERTYmp(p_l32_g2)w w 3

TRACE PROPERTYmp(p_l45_g2)l l 3

TRACE PROPERTYmp(p_l45_g2)w w 3

TRACE PROPERTYmn(n_pg45_g2)l l 3

TRACE PROPERTYmn(n_pg45_g2)w w 3

TRACE PROPERTYmn(n_pd45_g2)l l 3

TRACE PROPERTYmn(n_pd45_g2)w w 3

TRACE PROPERTYmp(p_l83_g2)l l 3

TRACE PROPERTYmp(p_l83_g2)w w 3

TRACE PROPERTYmn(n_pg83_g2)l l 3

TRACE PROPERTYmn(n_pg83_g2)w w 3

TRACE PROPERTYmn(n_pd83_g2)l l 3

TRACE PROPERTYmn(n_pd83_g2)w w 3

TRACE PROPERTYmn(n_nvt_18_ef_ucfn)l l 3

TRACE PROPERTYmn(n_nvt_18_ef_ucfn)w w 3

TRACE PROPERTYmn(n_hvbpw_25p_ef_ucfn)l l 3

TRACE PROPERTYmn(n_hvbpw_25p_ef_ucfn)w w 3

TRACE PROPERTYmp(p_hvdnw_25p_ef_ucfn)l l 3

TRACE PROPERTYmp(p_hvdnw_25p_ef_ucfn)w w 3

TRACE PROPERTYmp(p_mvbpw_25p_ef_ucfn)l l 3

TRACE PROPERTYmp(p_mvbpw_25p_ef_ucfn)w w 3

TRACE PROPERTYmn(n_mvbpw_25p_ef_ucfn)l l 3

TRACE PROPERTYmn(n_mvbpw_25p_ef_ucfn)w w 3

TRACE PROPERTYmn(n_mv_25p_ef_ucfn)l l 3

TRACE PROPERTYmn(n_mv_25p_ef_ucfn)w w 3

TRACE PROPERTYmn(n_ssgbpw_ef_ucfn)l l 3

TRACE PROPERTYmn(n_ssgbpw_ef_ucfn)w w 3

TRACE PROPERTYr(rspd_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rsnd_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rsnpo_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rsppo_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rnpd_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rnnd_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rnnpo_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rnppo_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rnhr_g2_ef_ucfn)l l 3

TRACE PROPERTYr(rnhr_g2_ef_ucfn)w w 3

TRACE PROPERTYr(rsnwell_w200_g2_ef_ucfn)r r 3

TRACE PROPERTYr(rsnwell_w200_ef_ucfn)r r 3

TRACE PROPERTYr(rsdnw_eflash)r r 3

TRACE PROPERTYr(rspwell_eflash)r r 3

TRACE PROPERTYr(rsnd_ef_ucfn)r r 3

TRACE PROPERTYr(rspd_ef_ucfn)r r 3

TRACE PROPERTYr(rsnpo_ef_ucfn)r r 3

TRACE PROPERTYr(rsppo_ef_ucfn)r r 3

TRACE PROPERTYr(rnnd_ef_ucfn)r r 3

TRACE PROPERTYr(rnpd_ef_ucfn)r r 3

TRACE PROPERTYr(rnnpo_ef_ucfn)r r 3

TRACE PROPERTYr(rnppo_ef_ucfn)r r 3

TRACE PROPERTYr(rnnpo_fg_eflash)r r 3

TRACE PROPERTYd(dion_g2_ef_ucfn)a a 3

TRACE PROPERTYd(dion_g2_ef_ucfn)p p 3

TRACE PROPERTYd(diop_g2_ef_ucfn)a a 3

TRACE PROPERTYd(diop_g2_ef_ucfn)p p 3

TRACE PROPERTYd(dionw_g2_ef_ucfn)a a 3

TRACE PROPERTYd(dionw_g2_ef_ucfn)p p 3

TRACE PROPERTYd(dionhpw_mvn_ef_ucfn)a a 3

TRACE PROPERTYd(dionhpw_mvn_ef_ucfn)p p 3

TRACE PROPERTYd(dionhpw_mvtn_ef_ucfn)a a 3

TRACE PROPERTYd(dionhpw_mvtn_ef_ucfn)p p 3

TRACE PROPERTYd(dionhpw_hvn_ef_ucfn)a a 3

TRACE PROPERTYd(dionhpw_hvn_ef_ucfn)p p 3

TRACE PROPERTYd(diopdn_mvp_ef_ucfn)a a 3

TRACE PROPERTYd(diopdn_mvp_ef_ucfn)p p 3

TRACE PROPERTYd(diopdn_hvp_ef_ucfn)a a 3

TRACE PROPERTYd(diopdn_hvp_ef_ucfn)p p 3

TRACE PROPERTYd(diohpwdn_mv_ef_ucfn)a a 3

TRACE PROPERTYd(diohpwdn_mv_ef_ucfn)p p 3

TRACE PROPERTYd(diohpwdn_hv_ef_ucfn)a a 3

TRACE PROPERTYd(diohpwdn_hv_ef_ucfn)p p 3

TRACE PROPERTYd(diodnw_mv_ef_ucfn)a a 3

TRACE PROPERTYd(diodnw_mv_ef_ucfn)p p 3

TRACE PROPERTYd(diodnw_hv_ef_ucfn)a a 3

TRACE PROPERTYd(diodnw_hv_ef_ucfn)p p 3

TRACE PROPERTYc(mimcaps_g2_ef_ucfn)c c 3

TRACE PROPERTYc(onocaps_g2_ef_ucfn)c c 3

TRACE PROPERTYq(pnp_v50x50_g2_ef_ucfn)a a 3

TRACE PROPERTYq(pnp_v100x100_g2_ef_ucfn)a a 3

TRACE PROPERTYq(npn_v50x50_ef_ucfn)a a 3

TRACE PROPERTYq(npn_v100x100_ef_ucfn)a a 3

TRACE PROPERTYc(ncap_18_g2_ef_ucfn)nf nf 0

TRACE PROPERTYc(ncap_18_g2_ef_ucfn)lf lf 3

TRACE PROPERTYc(ncap_18_g2_ef_ucfn)wf wf 3

CELL COMPARISON RESULTS ( TOP LEVEL )

#######################

# ###

##INCORRECT#

# ###

#######################

Error:Different numbers of instances (see below).

Error:Connectivity errors.

LAYOUT CELL NAME:delay_pp07

SOURCE CELL NAME:delay_pp07

--------------------------------------------------------------------------------------------------------------

INITIAL NUMBERS OF OBJECTS

--------------------------

LayoutSourceComponent Type

--------------------------

Ports:78*

Nets:2924*

Instances:5116*MN (4 pins)

5715*MP (4 pins)

1616C (2 pins)

82*R (3 pins)

------------

Total Inst:13249

NUMBERS OF OBJECTS AFTER TRANSFORMATION

---------------------------------------

LayoutSourceComponent Type

--------------------------

Ports:77

Nets:1919

Instances:117*MN (4 pins)

106*MP (4 pins)

22C (2 pins)

22R (3 pins)

15*INV (2 pins)

22SDW2 (3 pins)

02*SUP2 (3 pins)

20*SMP2 (4 pins)

------------

Total Inst:3026

* = Number of objects in layout different from number in source.

**************************************************************************************************************

INCORRECT OBJECTS

**************************************************************************************************************

LEGEND:

-------

ne= Naming Error (same layout name found in source

circuit, but object was matched otherwise).

**************************************************************************************************************

INCORRECT NETS

DISC#LAYOUT NAMESOURCE NAME

**************************************************************************************************************

1Net 4OUT1_B

----------------------------------------------------

(SMP2)utput** missing connection **

M27(20.688,21.351):s

(SMP2):input** missing connection **

M8(4.320,20.550):g

M62(18.610,7.982):s** missing connection **

** missing connection **(SUP2)utput

MM6:d

** missing connection **(SUP2):input

MM4:g

** missing connection **MM0:d

(SDW2):input** unmatched connection **

M58(4.320,9.015):g

(SDW2)utput** unmatched connection **

M57(4.320,4.242):d

** unmatched connection **(SDW2):output

MM2:d

** unmatched connection **(SDW2):input

MM7:g

--------------------------------------------------------------------------------------------------------------

2Net 3OUT0_B

----------------------------------------------------

(SMP2):input** missing connection **

M9(4.320,22.791):g

(SMP2):output** missing connection **

M26(20.688,19.110):d

M61(18.610,4.242):d** missing connection **

** missing connection **(SUP2):input

MM5:g

** missing connection **(SUP2):output

MM3:d

** missing connection **MM9:d

(SDW2):output** unmatched connection **

M58(4.320,9.015):s

(SDW2):input** unmatched connection **

M57(4.320,4.242):g

** unmatched connection **(SDW2):input

MM2:g

** unmatched connection **(SDW2):output

MM7:d

--------------------------------------------------------------------------------------------------------------

3Net 15** no similar net **

--------------------------------------------------------------------------------------------------------------

4** no similar net **INB

**************************************************************************************************************

INCORRECT INSTANCES

DISC#LAYOUT NAMESOURCE NAME

**************************************************************************************************************

5M42(40.660,12.774)MP(P_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

6M43(40.660,19.014)MP(P_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

7M49(46.424,17.496)MP(P_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

8M50(46.424,21.236)MP(P_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

9M65(25.094,1.881)MN(N_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

10M66(25.094,8.121)MN(N_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

11M76(47.144,1.862)MN(N_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

12M77(47.144,5.602)MN(N_33_G2_EF_UCFN)** missing instance **

--------------------------------------------------------------------------------------------------------------

13(SMP2)** missing gate **

Transistors:

M26(20.688,19.110)MP(P_33_G2_EF_UCFN)

M8(4.320,20.550)MP(P_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

14(SMP2)** missing gate **

Transistors:

M27(20.688,21.351)MP(P_33_G2_EF_UCFN)

M9(4.320,22.791)MP(P_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

15** missing gate **(SUP2)

Transistors:

MM4MP(P_33_G2_EF_UCFN)

MM3MP(P_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

16** missing gate **(SUP2)

Transistors:

MM5MP(P_33_G2_EF_UCFN)

MM6MP(P_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

17** missing gate **(INV)

Transistors:

MI364MP(P_33_G2_EF_UCFN)

MI362MN(N_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

18** missing gate **(INV)

Transistors:

MI363MP(P_33_G2_EF_UCFN)

MI361MN(N_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

19** missing gate **(INV)

Transistors:

MI353MP(P_33_G2_EF_UCFN)

MI352MN(N_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

20** missing gate **(INV)

Transistors:

MI5MP(P_33_G2_EF_UCFN)

MI7MN(N_33_G2_EF_UCFN)

**************************************************************************************************************

INFORMATION AND WARNINGS

**************************************************************************************************************

MatchedMatchedUnmatchedUnmatchedComponent

LayoutSourceLayoutSourceType

-----------------------------------------

Ports:7700

Nets:181811

Instances:7740MN(N_33_G2_EF_UCFN)

6640MP(P_33_G2_EF_UCFN)

2200C(MIMCAPS_G2_EF_UCFN)

2200R(RNHR_G2_EF_UCFN)

1104INV

0022SDW2

0002SUP2

0020SMP2

--------------------------------

Total Inst:1818128

o Statistics:

1 passthrough source net was deleted.

102 layout mos transistors were reduced to 25.

77 mos transistors were deleted by parallel reduction.

16 parallel layout capacitors were reduced to 2.

16 parallel source capacitors were reduced to 2.

8 series layout resistors were reduced to 2.6 connecting nets were deleted.

o Initial Correspondence Points:

Ports:VDD_PAD VSS_PAD VPP PROGRAM IN OUT OUTB

**************************************************************************************************************

DETAILED INSTANCE CONNECTIONS

LAYOUT NAMESOURCE NAME

**************************************************************************************************************

(This section contains detailed information about connections of

matched instances that are involved in net discrepancies).

--------------------------------------------------------------------------------------------------------------

M61(18.610,4.242)MN(N_33_G2_EF_UCFN)MM0MN(N_33_G2_EF_UCFN)

s: 6s: IB1

b: VSS_PADb: VSS_PAD

g: 15** no similar net **

d: 3** OUT0_B **

** no similar net **g: INB

** 4 **d: OUT1_B

--------------------------------------------------------------------------------------------------------------

M62(18.610,7.982)MN(N_33_G2_EF_UCFN)MM9MN(N_33_G2_EF_UCFN)

g: 16g: INBB

d: 7s: IB2

b: VSS_PADb: VSS_PAD

s: 4** OUT1_B **

** 3 **d: OUT0_B

**************************************************************************************************************

UNMATCHED OBJECTS

LAYOUTSOURCE

**************************************************************************************************************

(SDW2)** unmatched gate **

Transistors:

M73(41.380,5.543)MN(N_33_G2_EF_UCFN)

M57(4.320,4.242)MN(N_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

(SDW2)** unmatched gate **

Transistors:

M72(41.380,2.802)MN(N_33_G2_EF_UCFN)

M58(4.320,9.015)MN(N_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

** unmatched gate **(SDW2)

Transistors:

MM8MN(N_33_G2_EF_UCFN)

MM7MN(N_33_G2_EF_UCFN)

--------------------------------------------------------------------------------------------------------------

** unmatched gate **(SDW2)

Transistors:

MM1MN(N_33_G2_EF_UCFN)

MM2MN(N_33_G2_EF_UCFN)

**************************************************************************************************************

SUMMARY

**************************************************************************************************************

Total CPU Time:0 sec

Total Elapsed Time:0 sec

LVS OPTION中设定好电位

有的时候是一个充分非必要条件,如果能过就不用加,加了能过也不是版图出错。

电源本来就要写到lvs power name /lvs ground name 里面去的啊,

要不然怎么做erc分析么, 就没有参考电位了

电源本来就要写到lvs power name /lvs ground name 里面去的啊,

要不然怎么做erc分析么, 就没有参考电位了

学习了