Calibre PEX寄生参数提取后的spef文件在PT中分析的问题

我记得PEX出来的spef里面hierarchy带/X(不是很确切),要去掉

谢谢涛大~我在想是不是我在PEX提取的时候不用该选transistor level而应该选gate-level或者hierachy,因为PT中用于分析的网表文件是门级的、全是standard cell,所以抽取到晶体管级的话自然会产生不对应的情况,但是选gate-level或者hierachy又要提供h-cell文件,不知道这个文件上哪里找?或者这个文件在LVS过程中就产生了?

应该选gate-level,

缺少的文件到哪里找,我也不知道

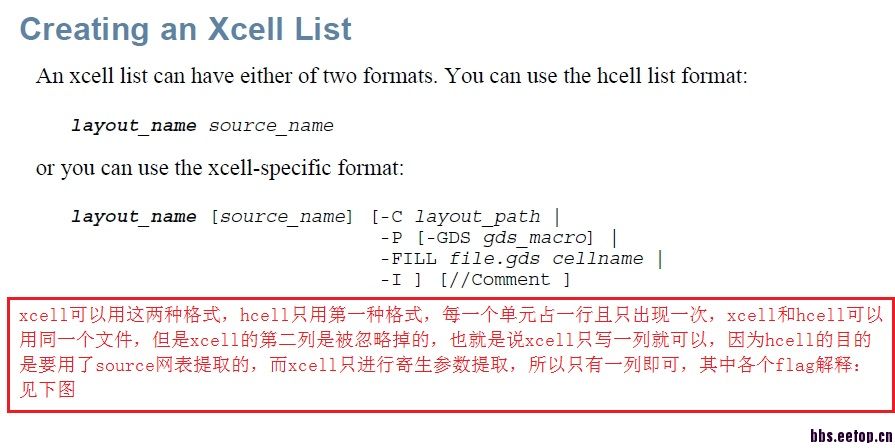

hcell自己写一个就可以了,把所有std cell和MACRO IP的名字重复下就好了

嗯我自己写了一个hcell的列表,设置的gate level和SPEF+PRIMETIME格式,PEX可以输出了,可是生成SPEF后导入到Prime Time中报错,内容基本上就是PT使用的verilog网表中找不到SPEF中对应的网络标号,请教各位大侠是什么原因呢?我PT中用的verilog网表是ICC布局布线之前使用的网表文件。

应该用ICCPR出来的。v

我看了在icc中p&r完以后用write_verilog输出的.v网表,net也没有这么复杂,跟p&r之前的差不太多,请问是我输出.v的时候还要进行什么设置吗?

眼睛能看出不同?

你的设计不会只有几个cell吧。

可以看.v里面的net信号的定义,比spef里面的net数量少很多。设计不大,cell不多,只是我来走设计流程的一个小模块。

我看了一下,Calibre PEX提取出来的SPEF文件的网络名部分如下:

========================

*NAME_MAP

*1Data_In[0]

*2Data_In[1]

*3Data_In[2]

*4Data_In[4]

*5VDD

*6VSS

*7Data_Out[0]

*8Data_In[6]

*9Data_Out[6]

*10Data_Out[1]

*11Data_In[7]

*12Data_Out[7]

*13Data_Out[5]

*14Data_Out[8]

*15Data_In[3]

*16Data_Out[10]

*17Data_Out[11]

*18Data_In[5]

*19Data_Out[13]

*20Data_Out[15]

*21Data_Out[12]

*22Data_Out[14]

*23Data_Out[4]

*24Data_Out[2]

*25Data_Out[3]

*26Data_Out[9]

*27Clk_In

*28N_Rst_In

*29Init_In

*30U53/M1

*31U53/M4

*33crc_shift_reg_reg[12]/M7

*34crc_shift_reg_reg[12]/M24

*35........

*36........

========================

红色标记的这些信号其实是CELL内部的网络信号,按照本意应该是没有的(verilog网表里面没有这些信号),请问各位大侠是我提取过程中有什么地方没注意吗?(PEX中我的设置是设置的gate level和SPEF+PRIMETIME格式)

但是不知道为什么会存在

多了没有关系,别少就行了

但是涛大,在primetime里面它会报类似下面的错:

Error: Cannot find port/pin 'crc_shift_reg_reg[12]/M7' in design

应该是verilog网表里面没有这些信号而导致的,不知道怎么解决。

用不着的东西,在verilog网表里面找不到就找不到呗

用report_annotated_parasitics看一下结果,如果都反标了就行了

Calibre不能抽gate level的spef吧, 建议LZ还是用S公司Star-RCXT和C公司Fire&Ice做这些事吧。

恩多谢涛大和chris的解答~

把calbire的runset贴出来,应该是你没有提取好。这种低级错误

同样的问题阿,小编问题解决了没有呢,坐等大神啊

您好,最近在提参数,要门级的,请教一下hcell文件怎么写呢,谢谢了

请教一下那个hcell文件怎么出来的,谢谢呀

学习一下,

同样的问题,抽的spef带晶体管,请问小编的问题解决了吗?谢谢!

请问您用calibre pex 给PT抽spef的问题解决了吗?我遇到了同样的问题,抽出的spef带有晶体管。谢谢!