求助!encounter进行P&R后,clkgate holdtime 不满足

时间:10-02

整理:3721RD

点击:

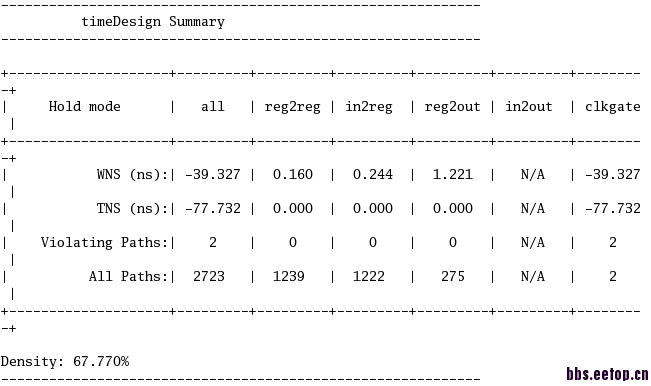

利用encounter进行P&R后,clkgate holdtime 不满足,如下图:

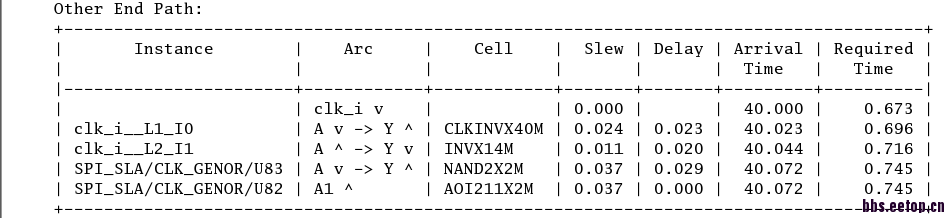

在encounter中进行时序分析,时序报告如下:

其中clk_i为系统主时钟,周期为80.由上图可以看出Arrival time为40,推测可能的原因是代码中采用了时钟的下降沿作为触发条件,附代码如下:

- always@(negedge clk_bus_i or negedge rst_n_i)

- begin

- if(!rst_n_i)

- cnt_odd_div_neg <= 3'b0;

- else

- cnt_odd_div_neg <= cnt_en?(cnt_odd_div_neg==bdry-1'b1)?3'b0 : cnt_odd_div_neg+1'b1 : 3'b0;

- end

- always@(negedge clk_bus_i or negedge rst_n_i)

- begin

- if(!rst_n_i)

- clk_neg_div <= 1'b0;

- else

- clk_neg_div <= cnt_en?((cnt_odd_div_neg==(bdry-1'b1)>>1) || (~|cnt_odd_div_neg))?~clk_neg_div : clk_neg_div : 1'b0;

- end

其中,cnt_en 在时钟上升沿产生的,clk_bus_i 直接与系统主时钟 clk_i 连接。这两段代码中由于需要必须要用 clk_bus_i的下降沿触发。

模块中其他语句用clk_bus_i的上升沿触发。

encounter进行PR后进行时序分析,仅剩两条clkgate的holdtime不满足。

在DC综合的约束中添加伪路径也不能解决此问题,百思不得其解,请各位高手帮助!

时钟路径的到达时间怎么是40ns呢?这个问题我也遇到过,门控时钟不大会用啊,我最后只好把门控去掉了,希望在此能有高人出来讲一下,俺也跟着学习学习!

建立小编把相关约束拉出来看看,这么大的hold违例,即使手工插buf也不太容易,我猜会不会是你的约束么做好吧。

clock gating 一般是tree固有的skew造成了。 控制一下gating 的位置吧

这是代码设计的问题,上升沿和下降沿混用了导致的半个周期的违例~

PR之后出现了许多hold违例,通过改约束基本都解决了,就剩下这两条了。试过许多改约束的方法,但是都无效。难道clkgate路径需要在约束中进行特别的设置吗,我觉得差半个时钟周期有点不科学啊

控制gating的位置是指修改代码吗?本人较菜,请多指点!

我也分析过代码,没发现有什么问题。请教一下,混用上升沿和下降沿会引起什么问题呢?

AOI211X2M要使用上升沿才行

encounter里面mode setup里面,可以设置不考虑clkgate的。

另外我觉得应该是false path 没设置吧。那个aoi211x2m 其中一个端口来自clki,另外一个端口来自前面的dffrqx2m,这个是需要constraint的么?

这个design频率不会是80ns吧?

小编,你这个问题后来是怎么解决的啊,我也碰到了一样的问题

约束肯定有问题啊

"encounter里面mode setup里面,可以设置不考虑clkgate的", are you sure?为什么我不可以。