请教关于rst信号的removal time 和recovery time 问题(已解决)

曾经在EDACN上面看到过这样一个问题:

“ removal time recovery time 定义为异步rst信号和clk信号之间的时序要求,

但有一点不理解,rst信号是异步的,如何保证其与clk之间的时序要求?

这项工作是在哪个阶段处理的?是在前端设计时要对异步rst信号进行什么处理吗?

还是在后端流程中工具会自动处理?谢谢“

有人回答1是:

如果DFF的异步rst和该DFF的时钟是异步的,那没有必要进行任何检查

如果DFF的异步rst和该DFF的时钟有相位关系,则需要进行removal和recovery的检查

其实就是分清楚了两个概念,带异步rst的DFF(rst和clk不一定是异步的),和异步电路

(只要相位没有关系就没有必要做timing检查)

还有人回答2是:

对rst同步的DFFRX的rst的removal是不需要做检查的,而同步之后q端输出到设计中的

DFFRX的rst却是需要做检查的,而且此时的removal是可以检查的,因为removal的撤销

时间是和clk有关系的。

我的疑惑是:

1、什么叫“如果DFF的异步rst和该DFF的时钟是异步的,那没有必要进行任何检查”?

这种情况会有吗?

2、对于回答2没能理解,请高人指点一二,谢谢!

1) 见FAQ

2)相当于Metastability DFF

1、FAQ中还是没能理解,希望通俗一点讲解,谢谢!

2、什么是“Metastability DFF”,能详细解释一下吗?或者有资料推荐一下,谢谢!

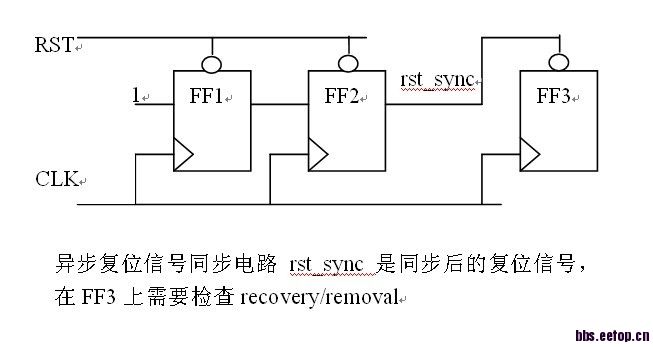

先弄清楚异步复位电路的复位信号怎么同步的,画了个图你看一下,这是标准的异步复位信号同步到时钟CLK的电路。FF1和FF2是同步器,不需要做Recovery/Removal检查,FF3 的复位信号是同步过的,需要检查。

图在这呢。

我觉得纯异步就是想象这种情况:

当rst信号由人手按按钮来给。

那么无论如何都有可能正好在时钟沿处变化,造成recovery/removal违例的。

这时就需要5#的两级DFF克服亚稳态的电路结构。

谢谢楼上几位牛人的讲解,终于弄明白了

几位的讲解都很精辟,膜拜ing....

学习一下,复位的设计很重要啊

网上看到的另外一个类似的解释

数字设计中很多新手不理解removal time \recovery time 的概念。<br>removal time \recovery time 类似于DFF的setup time \ hold time,不同之处在于前者是用来描述异步复位的。<br>一

般设计中,异步复位信号需要进行同步化处理,即让本来异步输入的复位信号,用时钟来锁存,这样本来和时钟没有相位关系的复位信号就和时钟用相位关系了。

STA时,如果DFF的异步rst和该DFF的时钟有相位关系,则需要进行removal和recovery的检查。removal和recovery检

查的目的是让DFF的异步rst信号在时钟沿附近满足建立\保持时间。当然,如果异步复位信号与时钟没有任何相位关系,则没有必要做removal

time \recovery time 检查。

学习了~

mark学习了

mark

这回算是弄懂了

楼上牛人

FF2的复位端是不是应该接长1 ?否则,FF1和FF2同时复位,接两个FF就没有意义了!

不知道理解的对不对。

常接1?接DFF1的输出更好?