求大神解答icc时候placement莫名的报错

我是根据lab guide 做的icc,placement的时候使用命令 place_opt –area_recovery -optimize_dft -power之后开始报错了

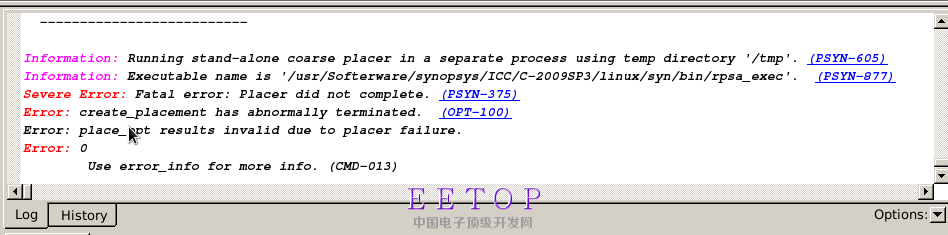

具体什么错误也不清楚,希望有了解的帮助一下 真心感谢[attachimg]651017

脚本运行后的错误提示

求助啊 很着急

怎么没有人帮忙解答一下啊

看看floorplan是不是有问题。看样子,像是place开始的时候floorplan有点问题。check一下floorplan,比如macro cell是否fixed,utilization是否过高(core面积太小),timing constraint是否过紧。都check一下,还有自己想到什么了也check一下。

其实我用的floorplan是指导里面直接给出的,应该没什么问题,我是想按照流程走一遍,看看每步的意义我现在担心的,是不是开始的链接库那里出了什么问题

check_physical_design -stage pre_place_opt -display 看看有什么错误

运行“check_physical_design -stage pre_place_opt -display”,后没有error,

但是有个警告“Can not decide the default browser, the result will not be opened by browser automatically.”我之前看过好像是需要更改主机IP什么的吗啊? 但是我没找到

另外,在最开始的时候还有两个

“Warning: Design 'ORCA_TOP' contains 1 high-fanout nets. A fanout number of 1000 will be used for delay calculations involving these nets. (TIM-134)

Warning: A non-unate path in clock network for clock 'SDRAM_CLK'from pin 'I_SDRAM_TOP/I_SDRAM_IF/sd_mux_dq_out_15/Z' is detected. (TIM-052)”

这个有影响吗

换个版本试试