tsmc 16nm encounter postroute drc violation 求助

时间:10-02

整理:3721RD

点击:

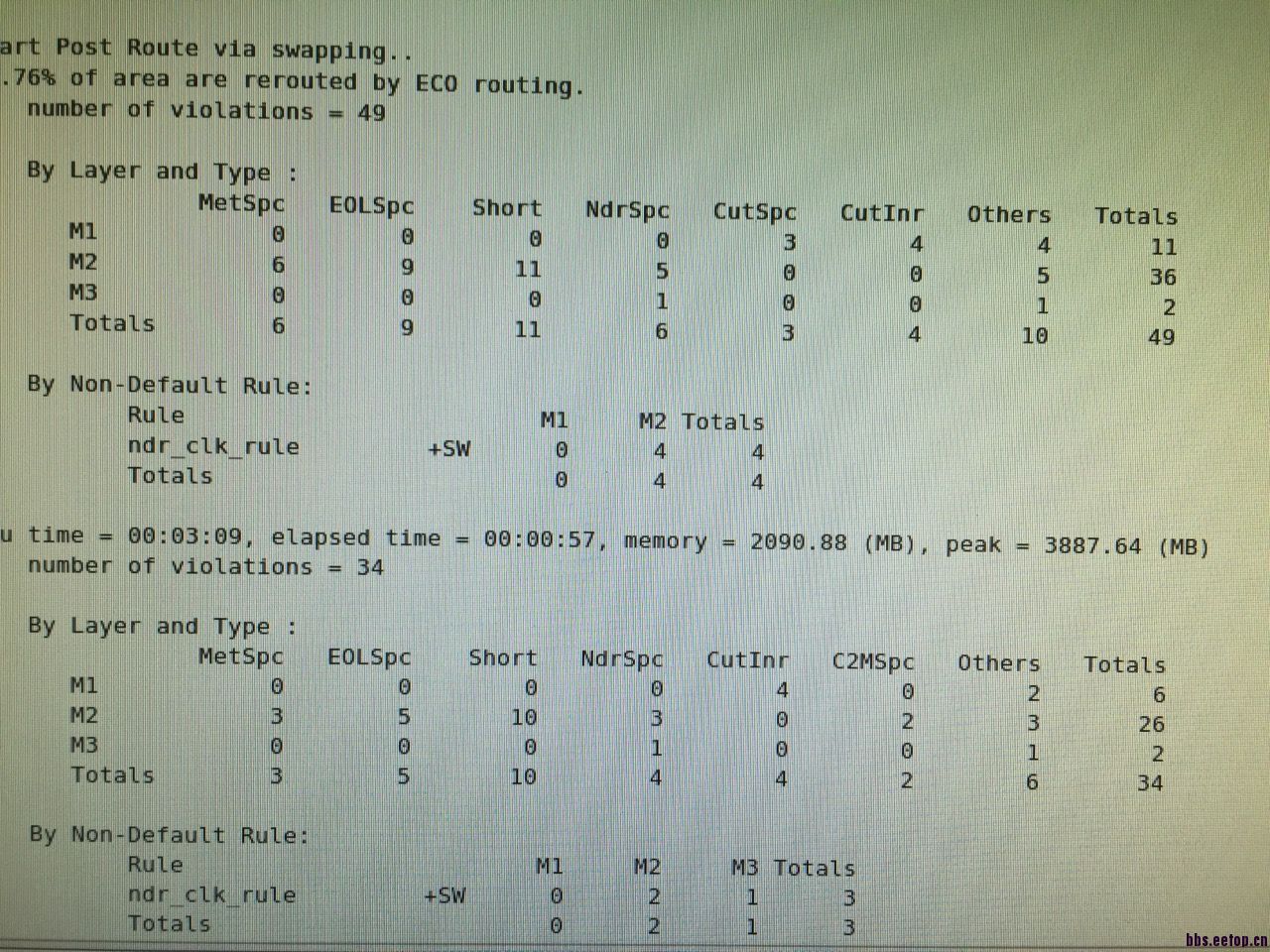

大家好,我刚刚接触tsmc 16nm 9 layer process ,我一个在p&R 数字模块,只用到6层金属,clock 用3~6 non default ,其它都是regular route ,post route 之后,

总是存在一些 drc 问题,gds write out 之后用calibre 检查不少metal space norch via 之类

的错误,按照我以前在90工艺中的经验,对于congestion还算可以的desgin,encounter p&r

部分应该route的很干净或比较干净,一些明显看上去不应该的为啥还存在呢? 有什么办法可以修掉这些?

ecoroute 几

次貌似还是搞不掉。

次貌似还是搞不掉。

刚接触pr就做16nm finfet,让人羡慕

28以后,router drc就多了,别提16了,再研究下吧

han .......

跟double pattern有关系吗,好高端不了解

16nm DRC rule研究了吗?16nm工艺DRC要求更严格,是否和楼上所说避免odd circle有关的DRC

好好看看design_rule,都有描述啊

好像是double pattern,出pin方向好奇怪

cool.