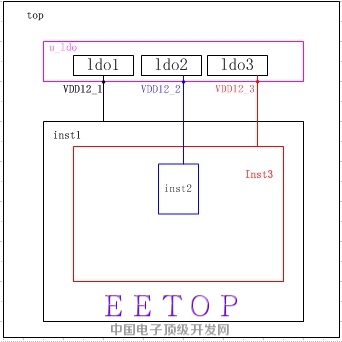

upf电源port定义问题请教

这种情况下,upf中我该如何定义电源的port(create_supply_port地冠以到哪里)?

这个port 本身也是虚拟的,不过要最后拉到top level的,你的3个power 肯定也是需要拉到top上的

你就当是top的port好了, 继续写吧

create_power_domainTOP -include_scope

create_power_domainPD1_inst1 -elementinst1

create_power_domainPD1_inst2 -elementinst2

create_power_domainPD1_inst3 -elementinst3

create_suppoly_portVDD1

create_suppoly_portVDD2

create_suppoly_portVDD3

create_suppoly_portVDD_TOP

非常感谢,之前一直理解这个本身没有port,该怎么定义。现在终于搞明白了,

电源port本身就是个全局port,只要保证LDO的输出与定义的port连在一起就行了

我向续问一个问题?

设计中我已经把所有的pg_pin的连接关系在rtl 上已经连接好了(port也连接好了),dc的时候可以不需create_supply_port去定义这个power port了,dc中命令add_port_state也能够识别这个power port。但是在formality的时候,add_port_state却不识别,这个有解释吗?而一旦我加上create_supply_port的定义,formality会报这个port已经存在了。

同时关于上述ldo内部产生的电源,我们可以在ldo 的lib 中定义internal_power的pg_type类型,也可以不再定义这个power 的port。

通常rtl不用写电源连接关系,全部电源关系用 upf 来描述比较好,

power port肯定是在后端derive到top level的,就像普通设计一样,VDD/VSS就是个虚拟概念,后端知道它的产生,但是前端不需要知道它的存在