setup time 和 hold time 两者之和为什么必须为正

就像下面解释hold time可以为负一样,形象解释下:

如果理想情况,hold肯定是一个正值,比如0.3,也就是前后级寄存器之间delay必须大于0.3。现在时钟树建完后有skew,前后寄存器的时钟差有正,有可能为负。

现在打个比方,后一个寄存器的时钟比前一个早到0.3,那么即使两级之间没有delay,就是任何情况都可满足hold检查,即hold为0。如果理解了这个,hold为负就不难理解了。后一个寄存器的时钟比前一个早到时间大于0.3,比如早到0.4,那么hold就是-0.1。

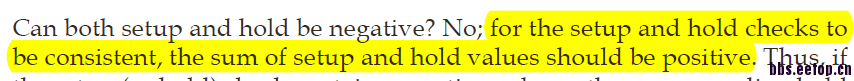

因为采样窗不可能为负

你好,能否详细说一下;

什么是采样窗,工具是如何利用采样窗来检查setup和hold的?

我只知道在分析noise的时候,有一个时间窗的概念!

先多谢了~!

http://www.ict.kth.se/courses/IL2201/Course_Slides/2012Slides/L_8_9_Timing.pdf

19页

我看完这两幅图后还是一头雾水;

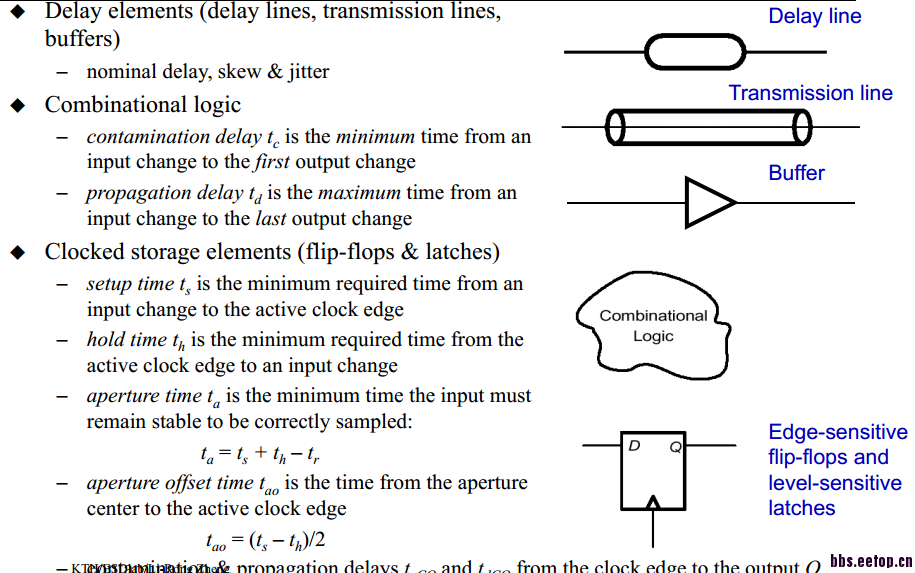

(1) 上面说的 tdcQ 说的是两级寄存器之间的逻辑电路的最大延迟吗?tccQ说的是两级寄存器之间的逻辑电路的最小延迟吗?

(2) 图中的tr又是什么?

(3) z最根本的一个问题,为什么要有一个采样窗口呢?

(4) from the aperture center to the active clock edge,那为什么是减去 th呢?

1)tdcQ应该是 最大的 时钟到数据的输出延时

tccQ 是最小的 时钟到数据的输出延时

2)tr传输时间 拉贝的书里边有

3)没看到 你说的‘z’

4)from the aperture center to the active clock edge 这句话后面 tao = (ts-th)/2 = (ts+th)/2-th

1)tdcQ应该是 最大的 时钟到数据的输出延时

tccQ 是最小的 时钟到数据的输出延时

2)tr传输时间 拉贝的书里边有

3)没看到 你说的‘z’

4)from the aperture center to the active clock edge 这句话后面 tao = (ts-th)/2 = (ts+th)/2-th

(3) 多打了个字母z,后面的是问题

(4) from the aperture center to the active clock edge (ts+th)/2 这个是aperture center为什么减去 th就是到 active clock edge了

(5) tdcq-tccq 这个差值有什么意义

没看懂, 为啥要加起来为正,

手册上提到的!

对于一个最小的基本的时序单元来说,setup就是在采样之前数据必须稳定的最小时间,hold就是采样之后数据必须稳定的最小时间。所以对于这样的基本单元,数据必须要稳定的最小时间是setup time + hold time.

对于一个复杂的时序单元,我们在建模的时候允许有负的setup time或者负的hold time。这是因为单元里面clock path和data path的长度不一样而已,但是这并不影响复杂单元里面最基本的采样单元的setup/hold time。 如果一个变负的值,对应的另外一个正值就会变得跟大,为了保证有一个最小的采样窗口(setup + hold),他们两个的之和必须为正,否则这个数据就不存在,所以也就采不到需要的数据了。

楼上说的应该是小编需要的答案,这个是和基本时序单元的库定义里的liberty setup time和liberty hold time定义有正有负的意思一样的吗?

这个是和基本时序单元的库定义里的liberty setup time和liberty hold time定义有正有负的意思一样的吗?

过来学习

恩 解释的很好,多谢!

为了保证有一个最小的采样窗口(setup + hold)

上面的意思也就是说对于一个最基本的时序cell,至少要让数据稳定一段时间才可能采到数据,否则数据不会被采到!

setup 、hold为负有什么优缺点?

setup time和hold time不是相反数吗,加起来不是为零吗?