关于cross clock domain (fast to slow)的一个小问题

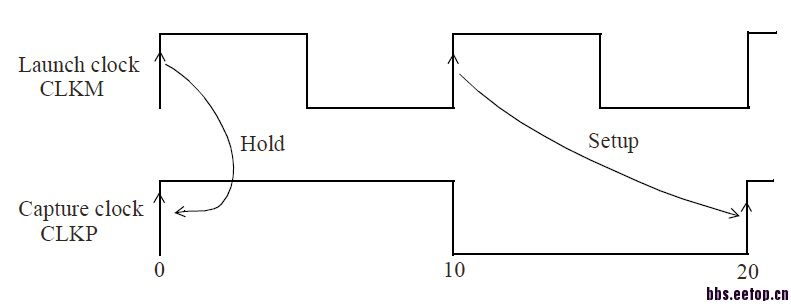

create_clock -name CLKM \

-period 10 -waveform {0 5} [get_ports CLKM]

create_clock -name CLKP \

-period 20 -waveform {0 10} [get_ports CLKP]

请问:CLKM第一个时钟沿发出的数据,是由CLKP的哪个时钟沿来接收的呢?

clkm的第二个时钟沿产生的数据会把第一个时钟沿产生的数据冲掉,所以这个要根据设计去合理设计multicycle path.

您的意思是如果design中有上面这样的时钟,并且不设置multi cycle的话,design就不正确了 是吗?

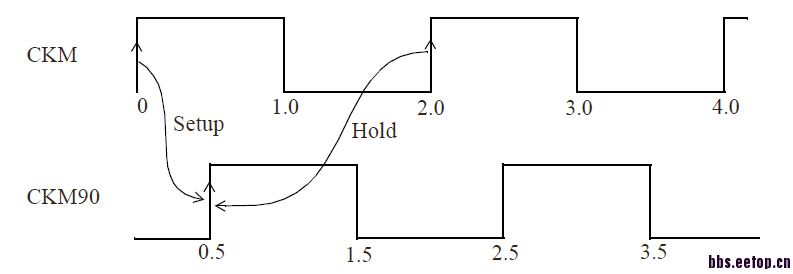

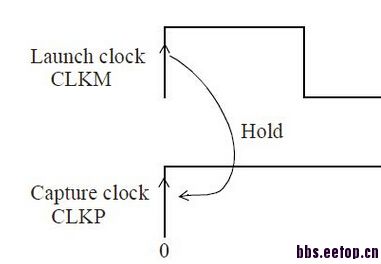

对于上面这种设计,比容容易理解 ;CLKM的第一个时钟沿发射的数据被CLK90第一个沿接受,hold的检查就是保证 CLKM的第二个时钟沿发射的数据不能太快传到CLK90处的寄存器,所以hold检查是CLKM第二个时钟沿与CLK90第一个时钟沿;

但对于第一图中的hold检查不是很理解,

其实我的意思就是说:hold检查的话,capture edge 必须是在 setup 检查时作为capture edge的时钟沿才可以吧

如第二幅图中,但第一幅图中 hold 的 capture edge 并没有在 setup check时作为capture edge啊

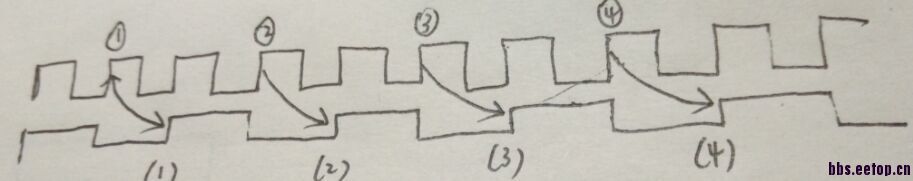

我觉得hold检查的应该是④和(3) 之间做检查才对啊

2个clock domain之间的sta就是 用最严的edge来算的, sta工具会帮你考虑的

你只要判断是不是real path,有必要可以设mcp或者false path,

hold的检查简单理解就是为了让 launch clock的第二个时钟沿发射的数据不把launch clock的第一个时钟沿发射的数据覆盖掉;

对于上图,把③看成launch clock的第一个时钟沿把④看成launch clock的第二个时钟沿,那么应该是④这个时钟沿发射的数据

不能把③这个时钟沿发射的数据覆盖掉嘛,而③发射的数据是由(3)来接收的,所以hold的检查 应该是④与(3)之间检查才合理;

如果按照工具默认的按最严来检查,那就变成0ns和0ns之间时候检查了,但这个明显没有意义啊

1#中的图,CLKM第一个时钟沿发射的数据是由CLKP哪个时钟沿来接收呢?

首先需要明确的是所有的约束都是根据design的功能来写的。只有知道degin的功能才能确定是不是false path, multicycle path, 以及如何设置multicycle path.

其次pt只有在确定了最严的setup的时钟关系之后,才能确认对应的hold check的时钟关系。

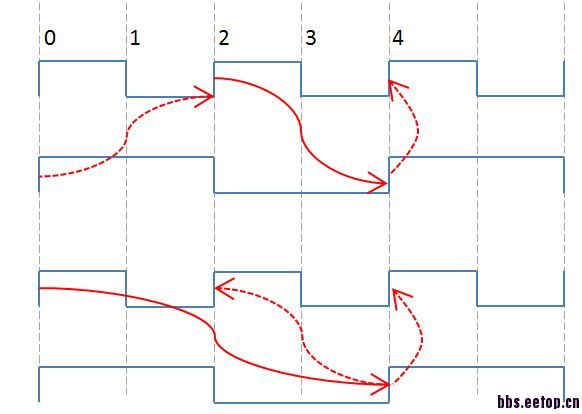

一般对于一个确定的setup check, 至少存在以下两个可能的hold check:

1. launch clock的下一个触发沿与capture clock 之间的check

2. launch clock和capture clock的前一个沿之间的check.

pt会在这两个检查之间选择一个最严的来检查hold.

如图, 默认 2-> 4之间的检查是最严的setup的检查 (setup 用实线表示, hold用虚线表示)。

对应有两个hold 检查。一个是 4 -> 4之间的检查,一个是2-> 0之间的检查。很明显 4->4 (等效于0->0)之间的检查是最严的。

所以默认pt会选择着这两个时钟沿来检查hold.

如果你通过设置multicycle改变了setup的check.那么对应的hold check之间的关系也会改变。

这个时候很明显2->4之间的hold检查比4->4之间的检查严,而且明显是不正确的。

所以我们在设置multicycle path的时候往往setup/hold都是成对出现的。

您好,我想问下,对于您贴的这个图来说,上半部分中,0时刻的launch edge发射的数据是被下面哪个时钟沿来capture的

我只是从sta分析角度列出来有那些可能的capture的edge.具体你要看你的design怎么设计。

如果只是从图上来看, 0 时刻发的数据是抓不到。

如图中所述:如果0时刻发射的数据不会被接收,那就没有必要用这个launch edge来检查hold啊?

hold是为了让当前launch edge发射的数据不会把前一个launch edge发射的数据覆盖掉;既然当前这个launch edge(如0时刻)

发射的数据不会被接收,也就是说不会将前面时钟沿的发射的数据覆盖掉;那检查这两个沿之间的hold没有意义啊

对应有两个hold 检查。一个是 4 -> 4之间的检查,一个是2-> 0之间的检查。很明显 4->4 (等效于0->0)之间的检查是最严的。

额 ,可能我还是没有说明白:

首先,hold check是为了让当前launch edge发射的数据不会把前一个launch edge发射的数据覆盖掉;

然后,如果用 4(lanuch)->4(capture) 来检查hold的话,因为4(launch)这个沿发射出去的数据不会被第二级寄存器任何一个时

钟沿来接收

最后,也就是说4(launch)这个沿根本没有必要做hold检查,因为它发射的数据不会覆盖任何其它沿发射的数据

首先你要明确sta工具是不关心功能的,他只是按照你的约束去做timing 检查而已。如果你默认什么约束都不给,那么他就按照我的图的上半部分去做检查。

第一步是确定哪两个沿之间的setup检查是最严的,然后根据这两个时钟沿按照我前面帖子里面的原则去选择选择一个最严的hold检查的时钟关系。

图里面所示,就是4->4之间的检查对于hold来说是最严的。之所以sta工具报出来的是0->0,而不是4->4是因为这两个沿在sta工具看起来是完全等效的而已. 没有必要在launch和capture clock上都加一个时钟周期而已。

我想了想,应该是这样的:

setup的检查没问题,也容易理解;对于hold check来说,如果不设置约束,工具检查的是 min{launch像右移动一个时钟沿,capture不懂;launch不懂,capture向左移动一个时钟沿}

这个就是工具分析是实际电路中不同,工具分析总是按照保守来计算,就像noise对时序的影响,noise有可能使时序变好,但是工具分析noise的时候,总是按照时序变差来分析;

多谢你了!

你好啊,我又想了下,觉得还是存在一些问题

“第一步是确定哪两个沿之间的setup检查是最严的,然后根据这两个时钟沿按照我前面帖子里面的原则去选择选择一个最严的hold检查的时钟关系”

如你上面所说,sta工具检查hold选择两者其中一个较为严格的,但较为严格的并不一定在真实的电路中存在的,如检查hold的时候用的是capture1 edge,但在电路中hold真实的检查应该用capture2 edge;

照这样看来,sta分析之后,即使hold有违例,实际电路也可能是没问题的;

分析一下有违例的hold路径,如果发现和上面说的一样,即工具检查的capture沿和时间的capture沿不一样,因为工具是按照最严的去检查,那是否可以说明我这条path不用fix了呢?

你不能脱离setup去谈hold.