异步复位同步释放电路后端处理方案

时间:10-02

整理:3721RD

点击:

网上关于复位信号的各种方式及其优缺点对比的资料很多,在电路设计中,我觉得大致可以这样分类使用:1. 电路中没有反馈,且对复位的实时性要求不高:使用异步复位方式;

2. 对复位时间的长短有较严格的要求:考虑使用同步复位方式;

3. 电路中带有反馈,且对实时性要求较高:考虑使用异步复位同步释放;

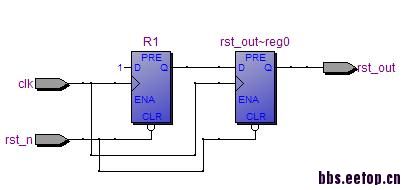

异步复位同步释放的一种方法:

在后端的处理中:

1. 同步复位作一般同步电路处理;

2. 异步复位作High-fanout处理;

3. 异步复位同步释放的方式则既有时序考量又需进行high-fanout处理,所以后端处理较为麻烦。其处理难点体现在如下部分:

a).在做fanout处理的时候,势必要插入buffer tree,导致复位信号到寄存器复位段的延迟加大;

b).时钟树本身存在很大的延迟;

如若算上clock tree延迟以及reset tree延迟,即rst_n(port)-->clock_tree-->reset_tree-->reg/CDN那么复位信号路径太大,而且时序势必更难收敛。

我想可能的处理方法如下:

1. 将异步复位同步释放部分的寄存器CP端设为 exclude pin,那么时钟不对该部分进行balance,从而使路径clock部分延迟大减;

2. reset_tree部分设置多周期路径,以使时序容易收敛;(但这样时钟频率变化可能会导致时序不满足吧)

这些只是以我个人的经验和看法,请各位帮忙指出其中的不足,也欢迎大家提出你们的解决方案!

2. 对复位时间的长短有较严格的要求:考虑使用同步复位方式;

3. 电路中带有反馈,且对实时性要求较高:考虑使用异步复位同步释放;

异步复位同步释放的一种方法:

在后端的处理中:

1. 同步复位作一般同步电路处理;

2. 异步复位作High-fanout处理;

3. 异步复位同步释放的方式则既有时序考量又需进行high-fanout处理,所以后端处理较为麻烦。其处理难点体现在如下部分:

a).在做fanout处理的时候,势必要插入buffer tree,导致复位信号到寄存器复位段的延迟加大;

b).时钟树本身存在很大的延迟;

如若算上clock tree延迟以及reset tree延迟,即rst_n(port)-->clock_tree-->reset_tree-->reg/CDN那么复位信号路径太大,而且时序势必更难收敛。

我想可能的处理方法如下:

1. 将异步复位同步释放部分的寄存器CP端设为 exclude pin,那么时钟不对该部分进行balance,从而使路径clock部分延迟大减;

2. reset_tree部分设置多周期路径,以使时序容易收敛;(但这样时钟频率变化可能会导致时序不满足吧)

这些只是以我个人的经验和看法,请各位帮忙指出其中的不足,也欢迎大家提出你们的解决方案!

现在不都是异步复位同步撤离么, 后端没太多讲究 , 只要把reovery/removal check打开就行了

2级同步flop放的近一些, reset hfn是自动工具会解开的,没啥