陈版主,各位大侠:帮一下忙啊:下面的sdc文件写的对不对啊?

第一次学习用soc encounter做P&R时,生成的SDF文件在后仿出现errors

步骤:

按照上面的步骤的说法,执行了(1)(2)(3)(4)步,

第(1)步是

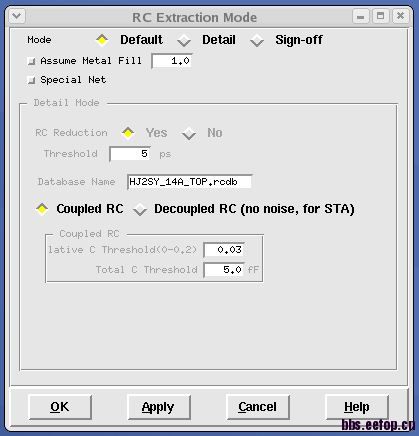

第(2)步见上面的流程图

第(3)步是

第(4)步见上面的流程图

后仿出现的errors:

# ** Error: (vsim-SDF-3262) D:/test_for_ph/HJ2SY_14A_TOP_20110721_pm.sdf(5893): Failed to find matching specify timing constraint.

# ** Error: (vsim-SDF-3262) D:/test_for_ph/HJ2SY_14A_TOP_20110721_pm.sdf(5919): Failed to find matching specify timing constraint.

# ** Error: (vsim-SDF-3262) D:/test_for_ph/HJ2SY_14A_TOP_20110721_pm.sdf(5961): Failed to find matching specify timing constraint.

# ** Error: (vsim-SDF-3262) D:/test_for_ph/HJ2SY_14A_TOP_20110721_pm.sdf(5981): Failed to find matching specify timing constraint.

# ** Error: (vsim-SDF-3262) D:/test_for_ph/HJ2SY_14A_TOP_20110721_pm.sdf(5999): Failed to find matching specify timing constraint.

基本上是相同的errors

是不是第(1)(3)步都是默认设置,所以出错了啊?

还是需要在上面四步中设置一下选项啊?

或者是其他步骤的操作不对,引起了这一步骤生成的.sdf文件不对啊?

附上sdc文件,是不是要注销很多语句行啊?

###################################################################

set sdc_version 1.7

set_units -time ns -resistance kOhm -capacitance pF -voltage V -current mA

set_wire_load_mode enclosed

set_max_fanout 30 [current_design]

set_max_transition 1 [current_design]

set_max_area 0

set_driving_cell -lib_cell INVX2M -library ss_1v62_125c [get_ports I_por]

set_driving_cell -lib_cell INVX2M -library ss_1v62_125c [get_ports I_din]

set_driving_cell -lib_cell INVX2M -library ss_1v62_125c [get_ports I_clk]

set_load -pin_load 0 [get_ports O_decode_en]

set_load -pin_load 0 [get_ports O_decode_en_dly]

set_load -pin_load 0 [get_ports O_dout]

set_ideal_network -no_propagate[get_ports I_por]

set_ideal_network -no_propagate[get_ports I_clk]

create_clock [get_ports I_clk] -name I_clk -period 60-waveform {0 30}

set_clock_latency 3[get_clocks I_clk]

create_clock [get_pins SY01/dig_hj2sy/u_ee_inter/I_ck2]-name SY01/dig_hj2sy/u_ee_inter/I_ck2-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_ee_inter/I_ck2]

create_clock [get_pins SY01/dig_hj2sy/u_rf_pre/I_clock]-name SY01/dig_hj2sy/u_rf_pre/I_clock-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_rf_pre/I_clock]

create_clock [get_pins SY01/dig_hj2sy/u_rf_inter/I_rf_clk]-name SY01/dig_hj2sy/u_rf_inter/I_rf_clk-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_rf_inter/I_rf_clk]

create_clock [get_pins SY01/dig_hj2sy/u_data_pre/I_bit_clk]-name SY01/dig_hj2sy/u_data_pre/I_bit_clk-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_data_pre/I_bit_clk]

create_clock [get_pins SY01/dig_hj2sy/u_data_pre/I_ck128]-name SY01/dig_hj2sy/u_data_pre/I_ck128-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_data_pre/I_ck16]-name SY01/dig_hj2sy/u_data_pre/I_ck16-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_ctrl_clk/I_ck2]-name SY01/dig_hj2sy/u_ctrl_clk/I_ck2-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_picc_state/I_bit_clk]-name SY01/dig_hj2sy/u_picc_state/I_bit_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_cmd_par_dec/I_bit_clk]-name SY01/dig_hj2sy/u_cmd_par_dec/I_bit_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_cmd_state/I_bit_clk]-name SY01/dig_hj2sy/u_cmd_state/I_bit_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_main_ctrl/I_ac_clk]-name SY01/dig_hj2sy/u_main_ctrl/I_ac_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_main_ctrl/I_bit_clk]-name SY01/dig_hj2sy/u_main_ctrl/I_bit_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_ee_inter/I_rf_clk]-name SY01/dig_hj2sy/u_ee_inter/I_rf_clk-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_ee_inter/I_rf_clk]

create_clock [get_pins SY01/dig_hj2sy/u_ee_inter/I_bit_clk]-name SY01/dig_hj2sy/u_ee_inter/I_bit_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_parity/I_parity_inclk]-name SY01/dig_hj2sy/u_parity/I_parity_inclk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_crc/I_crc_clk]-name SY01/dig_hj2sy/u_crc/I_crc_clk-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_crc/I_crc_clk]

create_clock [get_pins SY01/dig_hj2sy/u_crypt/I_m1crypt_clk]-name SY01/dig_hj2sy/u_crypt/I_m1crypt_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_access/I_ac_clk]-name SY01/dig_hj2sy/u_access/I_ac_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_err_op/I_ck2]-name SY01/dig_hj2sy/u_err_op/I_ck2-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_err_op/I_bit_clk]-name SY01/dig_hj2sy/u_err_op/I_bit_clk-period 60-waveform {0 30}

create_clock [get_pins SY01/dig_hj2sy/u_ee_buf/I_buf_clk]-name SY01/dig_hj2sy/u_ee_buf/I_buf_clk-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_ee_buf/I_buf_clk]

create_clock [get_pins SY01/dig_hj2sy/u_uid_comp/I_uidcomp_clk]-name SY01/dig_hj2sy/u_uid_comp/I_uidcomp_clk-period 60-waveform {0 30}

set_clock_latency 3[get_clocks SY01/dig_hj2sy/u_uid_comp/I_uidcomp_clk]

set_input_delay -clock I_clk-max 16[get_ports I_clk]

set_input_delay -clock I_clk-min 4[get_ports I_clk]

set_input_delay -clock I_clk-max 16[get_ports I_por]

set_input_delay -clock I_clk-min 4[get_ports I_por]

set_output_delay -clock I_clk-max 16[get_ports O_decode_en]

set_output_delay -clock I_clk-min 4[get_ports O_decode_en]

set_output_delay -clock I_clk-max 16[get_ports O_decode_en_dly]

set_output_delay -clock I_clk-min 4[get_ports O_decode_en_dly]

set_output_delay -clock I_clk-max 16[get_ports O_dout]

set_output_delay -clock I_clk-min 4[get_ports O_dout]

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_pre/O_decode_en_reg] -from\

CK -to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_pre/O_por_reg] -from SN -to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_pre/O_por_reg] -from SN -to QN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/O_in_en_reg] -from CKN \

-to QN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/O_in_en_reg] -from CKN \

-to SN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/O_in_en_reg] -from CKN \

-to RN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/O_in_en_reg] -from CKN \

-to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/in_en_d128_reg] -from\

CKN -to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/in_en_d128_reg] -from\

CKN -to SN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/in_en_d128_reg] -from\

CKN -to RN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/in_en_d128_reg] -from\

CKN -to QN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/ck64_reg] -from CK -to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/ck2_reg] -from CK -to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/ck16_reg] -from CK -to Q

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/ck16_reg] -from CK -to \

RN

set_disable_timing [get_cells SY01/dig_hj2sy/u_rf_inter/ck16_reg] -from CK -to \

QN

set_disable_timing [get_cells SY01/dig_hj2sy/u_ctrl_clk/U21] -from A -to Y

非常感谢!

我的也出问题了,反标出现问题,类似下面的错误

SDFA Error: Could not find path C to Y in instance tst_dsm.dsm_pr_ins.U6

还不知道怎么改.

你用的是哪个版本.

我的是encounter 9.1

和搜到的教程都不太一样.

我的encounter很老,好像是6.1的

你有教材?可以分享一下吗?

我的资料是在eetop上下载的

跟你贴的图差不多,我在网上看到的.

基于hejian18工艺的SOC Ecounter数字版图设计流程

http://www.docin.com/p-158910271.html

它这个版本和我的也不一样.

弄的我现在都不知道得到的版图对不对.

我听说有的只输出spef做STA,然后导出sdf文件做后防

反正乱乱的,

跟你一起学习吧.

encounter出def

starRC读入,出SPEF

PT读入,出SDF,供后仿

那个error不是说sdc没找到吗!

为什么不能用encounter直接输出的sdf文件后仿呢?

有什么说法吗?

如果想signoff的话,你就得用标准流程,不然不准

帮写个标准流程吧,以及每步用的谁家的工具.

我大概说说我的情况

1.verilog 代码;产生*.v给DC;

2. DC 综合,生成*_syn.v 和*.sdc给encounter

3.encounter布局布线,生成*_pr.v,*.gds2,

4.formility, primitime, verilog simu.

具体说说encounter和它之后的每一步吧.

我现在可以做formility,

verilog simu. 反标文件有问题

primtime还没用过,准备去学了.

我觉得是我的.sdc文件不对啊。

有没有哪个大侠有关于写.sdc文件的资料啊?

非常感谢!

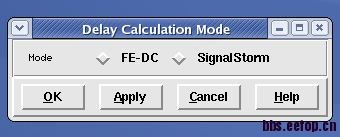

另外,第三步是不是没选FE-DC 或者是 SignalStorm啊?

各位大侠帮一下忙啊!

非常感谢!

我也是用5#的方法做的,但用你的方法做的话,不应该把ideal clock 选项打开吧?

你说的是要把:

#set_ideal_network -no_propagate[get_ports I_por]

#set_ideal_network -no_propagate[get_ports I_clk]

注消掉吗?

但是改了之后,还是不行啊?

想问个问题,ICC和Encounter的区别在哪?

用哪个作数字后端比较流行阿。

还要把