Conflict Non-Stop Pins解决方案

Conflict Non-Stop Pins

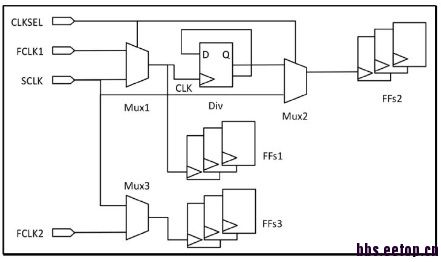

For a given design, typically there are at least two modes: afunctional mode and a test mode. Between those modes, conflicting clock pindefinitions may exist, as illustrated below.

In the functional mode, a generated clock is defined at pin Qof the clock divider, Div. This will result in a non-stop pin, Div/CLK, for thefunctional mode. However, in the test mode, a generated clock is not defined atDiv/Q. CTS tools will treat Div/CLK as a leaf pin or stop pin and try tobalance the path through Div with all of the other flops FFs1 and FFs2. This isneither possible nor something that designers want. Div is a clock divider andshould not be tested by scan, and hence, Div/CLK should be ignored.

The rightsequence of steps for a CTS tool is to first synthesize FCLK1 and FCLK2 in thefunctional mode. Next, in the test mode, set Div/CLK to be ignored andsynthesize SCLK.

最后的文字表示要做两轮的CTS,大家谁有经验吗?是用两个clock spec,跑完function mode再跑另一个test mode?

怎么通过审核以后,我插的图片不见了?!

继续求教!

:o

没有一个人知道啊,晕

跟我走吧,快点回家!

?

先做function mode的,test mode顶多多一些hold 问题,