get_pins疑惑,寻求帮助

时间:10-02

整理:3721RD

点击:

请教一下,get_pins的命令是用在DC综合脚本里面,还是用在PT脚本里面?

如果是DC综合脚本里面的话,那么例如set_dont_touch_network [get_pins MUX2/Y]

中具体的MUX2/Y位置,没有综合前,即没有网表,又怎么找到该位置呢。对此比较困惑,麻烦解答下,谢谢。

那么此时我有几个 hier boundary呢?

像2楼说的那样 应该不是hier boundary吧 但我觉得他说的挺对的,小编说的加在hier boundary上,怎么操作呢如果MUX2的输出Y端还是在笨模块内,没有接到其他模块,那怎么利用hier boundary呢? 还望小编大人抽点时间 讲解下

如果是DC综合脚本里面的话,那么例如set_dont_touch_network [get_pins MUX2/Y]

中具体的MUX2/Y位置,没有综合前,即没有网表,又怎么找到该位置呢。对此比较困惑,麻烦解答下,谢谢。

不知道小编是不是说在你的rtl中没有MUX2这个实例化单元,而是一个assign 语句来实现你需要的那个选择的功能。 assign Out_nam = (Condition)?(Select_name1)Select_name0),如这样的话,那么你是不知道综合工具会将该语句综合成什么名字的MUX单元的。所以这时,你就得找你的Code中找这个Out_name,看它和什么地方相连,看那些地方是否有一些register之类的器件,从而把你要的这个约束给设置上。

不知道我得解答能不能帮到你?

综合前,写在 hier boundary上, 综合后,可以写在instance pin级别

谢谢,很好的帮助,明白了。

谢谢,明白了

我想再向你请教下,如果在综合后,遇到max transition 和 max capacitance这类DRC违例,那么该主要从哪些方面考虑进行优化排除呢?先谢谢了

前端不用管,后端能修掉,

只要管管timing就行了

谢谢,也就是说前端有部分的DRC违反,只要后端PR部分可以修复就可以了,是吧

对,后端来修 max_fanout/max_cap/max_trans violation

谢谢!

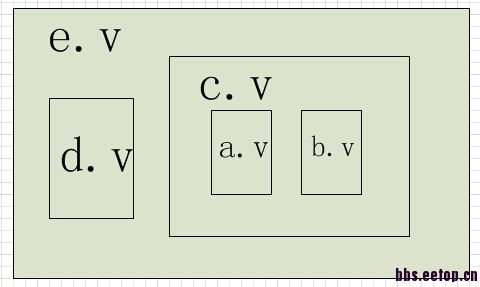

hier boundary?是不是说比如我有 a.v b.v c.v d.v e.v 然后c.v包含了a.v b.v ,然后e.v又包含了c.v d.v ,如下图所示:

那么此时我有几个 hier boundary呢?

像2楼说的那样 应该不是hier boundary吧 但我觉得他说的挺对的,小编说的加在hier boundary上,怎么操作呢如果MUX2的输出Y端还是在笨模块内,没有接到其他模块,那怎么利用hier boundary呢? 还望小编大人抽点时间 讲解下