求助:请问如何在virtuoso的shematic 包括 stdcell? (已解决,请看6楼总结))

小弟新人,刚用encounter生成netlist (savenetlist -phys xxx.v), 导入virtuoso生成schematic,也用了reference lib 作为标准单元库,但是发现schematic中的cell似乎没有调用标准库,因为log中出现:

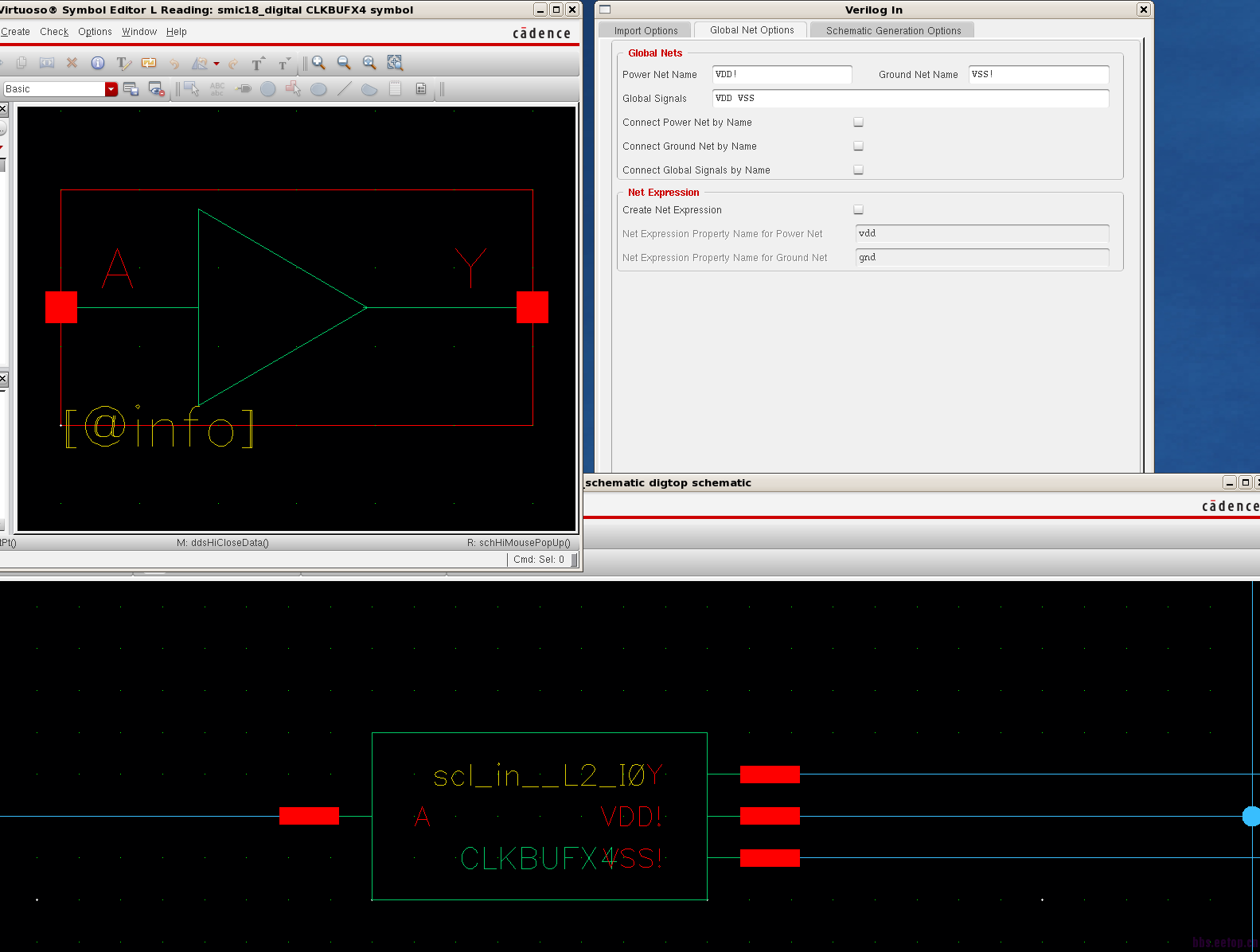

“Number of pins on symbol CLKBUFX4 in library xxx lib differ from the number of ports in

the HDL module description", 请问如何解决 (为了大家容易看明白,特附上图,下边是自己schematic的一个buffer,有四个Pin,其中输入A 输出Y 和左上角的标准库中的这个cell 一样,但是却还有 VDD! VSS!, 在这个std cell symbol中是没有的,导致的结果是我不能再查看这个buffer到更低一级,里面只有pin,没有transistor),另外,右上角设power, 到底怎么设呢?

除了 symbol view 还有没有其他 view 是包含power和ground的,把它 save as symbol view.

当然还有其他方法,不过说起来更复杂,具体看verilog in UG,名字忘记了, keyword 是 verilogin 或者 verilog in

感谢前辈回复,top cell的symbol view 是有的,然后这个top cell 的schematic 里的各个cell的symbol view 也有,cell之间也是有连线,感觉像模像样的。但是查看所有cell的MOS级,只剩下pin, 没有MOS, 没有连线,比如这个buffer, 在schematic里,显示为symbol view 有输入A, 输出B, VDD!和VSS!四个pin, 都连到其它cell或是power, 但是到MOS级只剩四个pin; 标准单元里的这个buffer, symbol view 只有输入A, 和输出B, 却没有VDD!和VSS!(当然,到MOS级,能看到VDD!和VSS!和所有改有的)

UG 我也看了,但是没有具体的介绍。

还请大家再帮帮忙。

谢谢

解决了,其实直接用encounter的GUIsave..生成.v用于schematic,不需要使用命令 savenelist 加什么option, 这样的.v既没有vdd!和vss!, 也没有什么filler之类的, 。然后记得在verilog in 时,填写正确的含有standard cell的reference library (foundry的PDKS里面有,表括std cell的layout和schematic等等), 这样就使得自己的cell里的sub module cell 和 std cell 的pin 的数量 match了。

希望总结对大家有用!也呼吁大家提完问题,如果最终有答案了,回来冒个泡update一下,方便别人查找。

直接用encounter的GUI生成.v, 里面就没有有VDD和VSS了 (之前用的 savenetlist -phys.....),然后verilog in, 成功

6楼怎么不出来,大家看7楼把,简单介绍。