关于自动布局布线后版图错误的问题

时间:10-02

整理:3721RD

点击:

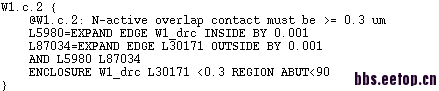

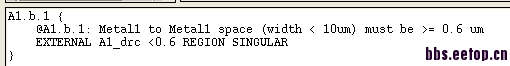

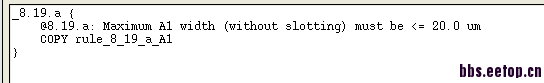

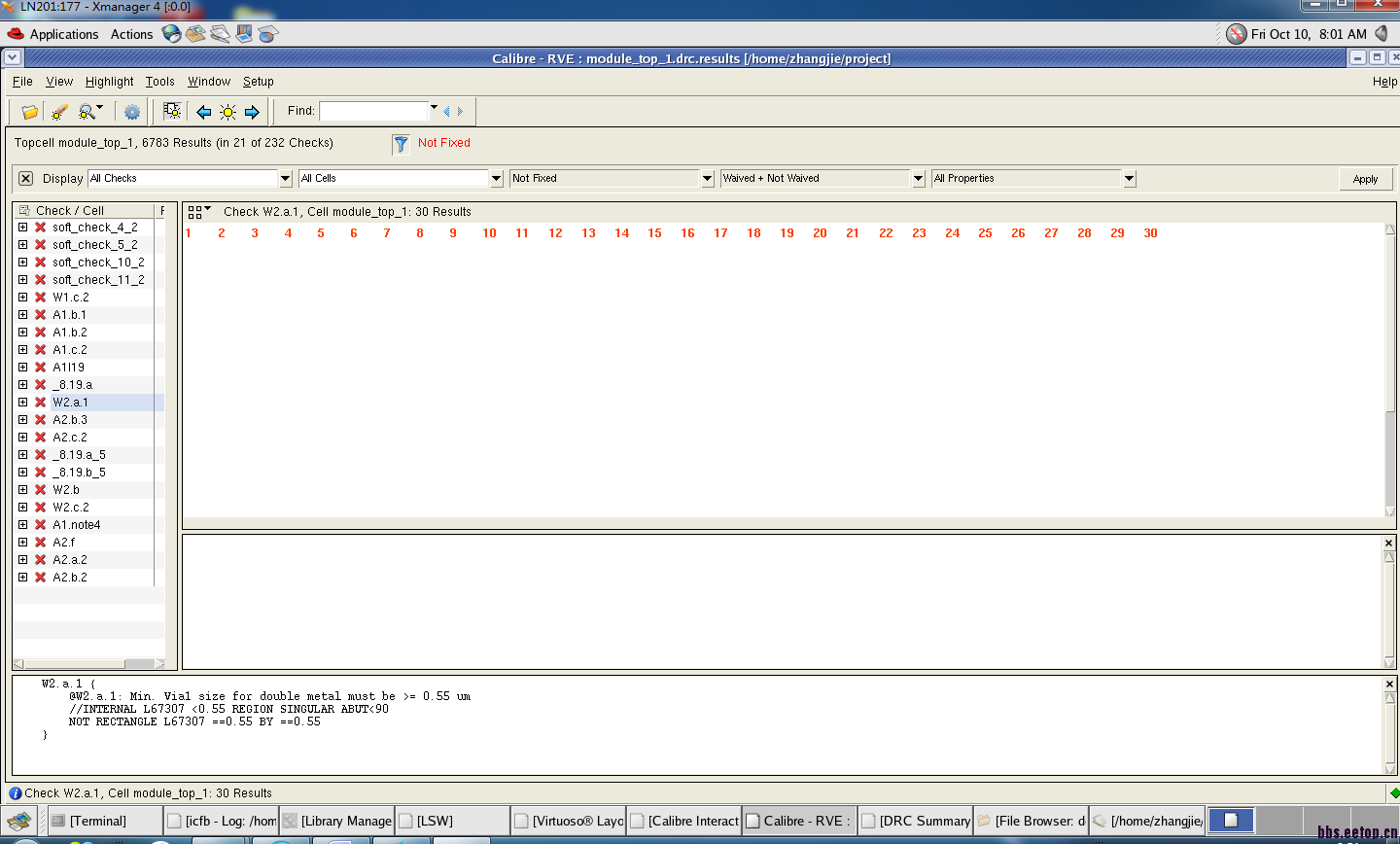

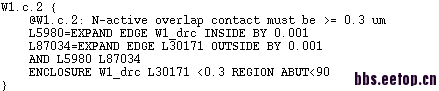

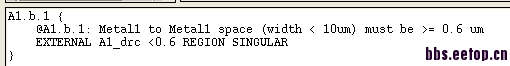

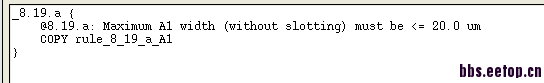

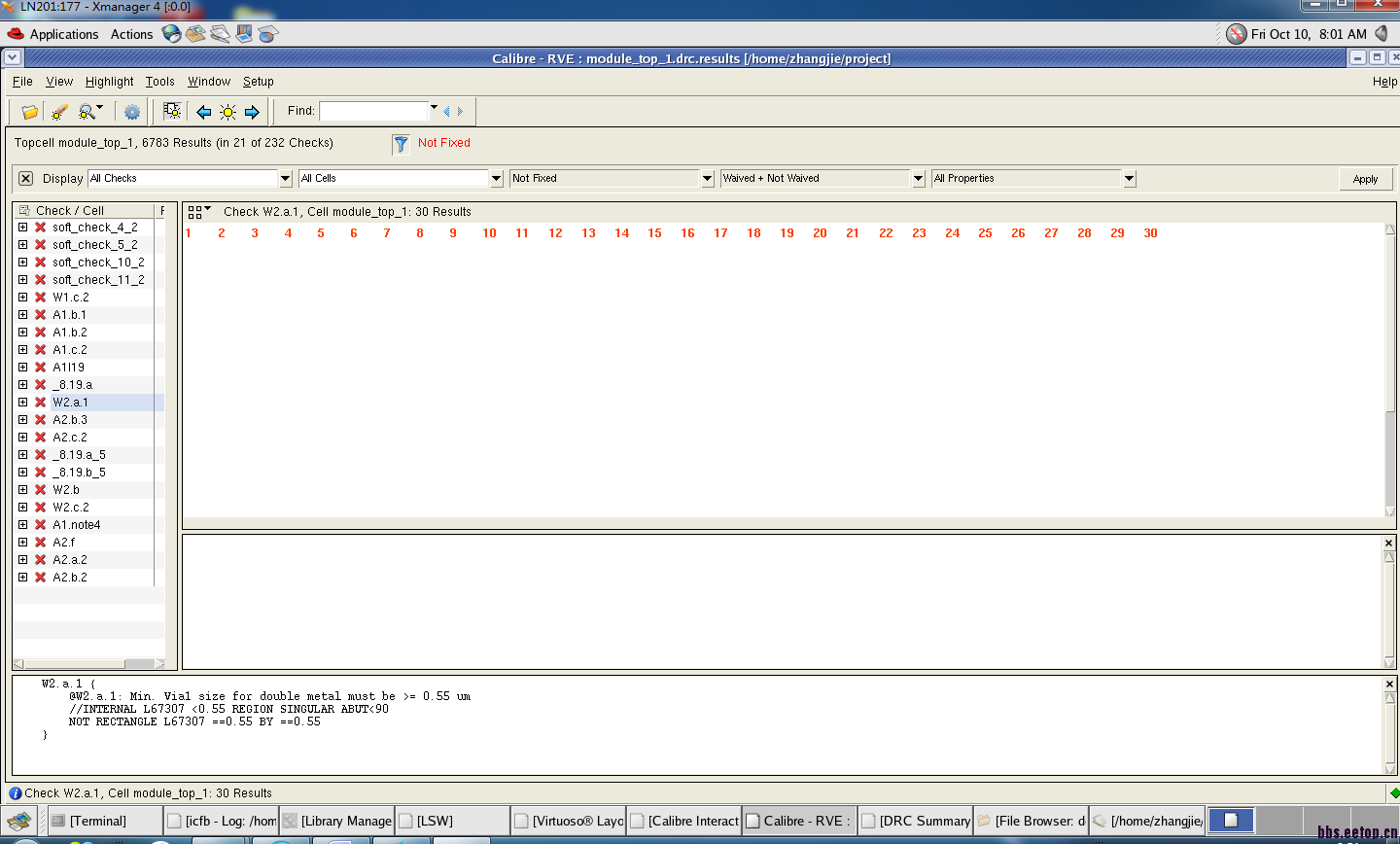

各位大神,你们好。我将.gds文件导入icfb后,DRC后出现了许多错误,错误少的有十几个,多的有上千个。手动修改肯定不可以的,请问大家遇到这种问题时该怎么解决呀?谢谢大家了。这是部分截图。

顶一下,大家支持一下啊。谢谢啦

gds是工艺厂给的吗?最好与工艺厂确认下有没有问题,工艺厂也会犯错

用到wide metal了,造成space问题。

soft的问题,不确定

最好看一下tf文件中的设计规则是否和设计规则检查文件一致?

工艺厂家一般不会及时更新tf文件,但是设计规则文件一般是最新的。

如果是tf问题,手动更改tf文件中的设计规则即可。不过得重新进行布线了。

请问tf文件怎么读啊?这是其中一段:VIA DIFF_M1

LAYER TO ;

RECT -0.550 -0.550 0.550 0.550 ;

LAYER W1 ;

RECT -0.250 -0.250 0.250 0.250 ;

LAYER A1 ;

RECT -0.550 -0.550 0.550 0.550 ;

RESISTANCE 2.500000e+01 ;

END DIFF_M1

这个0.55是什么意思啊?

谢谢大神们了

这段是定义了一个 M1到diff的contact,其中RECT -0.550 -0.550 0.550 0.550是一个正方形,左下角坐标在-0.55 -0.55,右上角坐标是0.55 0.55,也就是说边长为1.1的矩形,原点在中心点。

你最好先跑下lvs,确保导入导出的时候gds layer没有问题。看你的几个drc,前两个都是diff,nwell的问题,有点像是gds layer map不对(仅仅是猜测)。