calibre lvs碰到的一个问题

时间:10-02

整理:3721RD

点击:

]

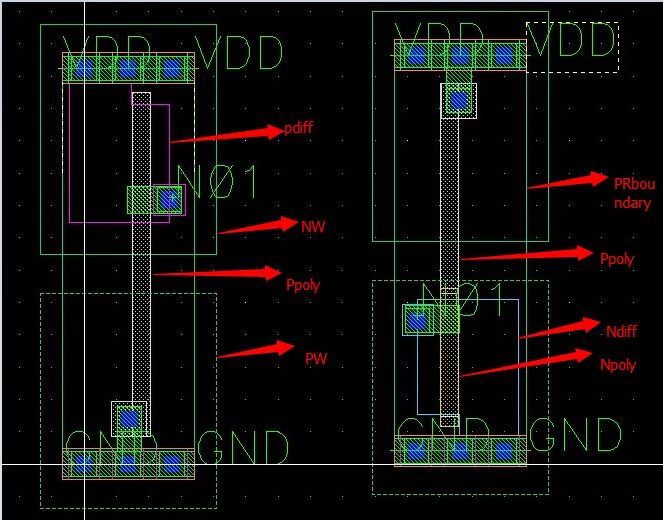

]

上图为tieh/l cell的版图,单独做lvs的时候都pass;现在做整个chip 的lvs,左边那个过了,右边的没过,请大家帮我分析一下是怎么回事。

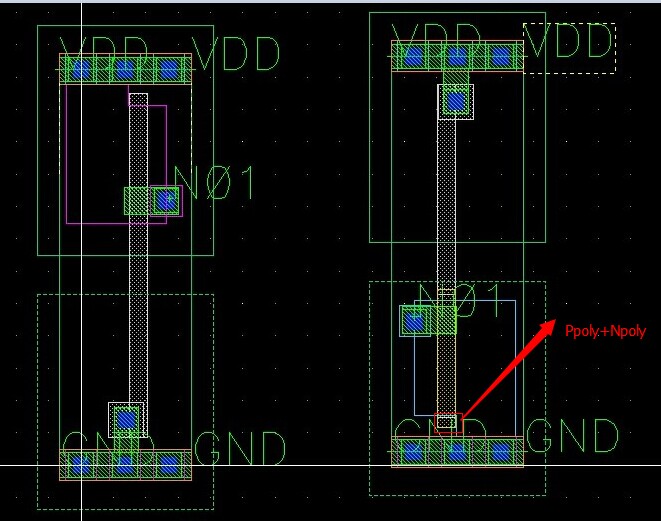

那个npoly和ppoly相叠加的部分,extract了个net 3,lvs的report里提示

layout:Source:

net 3GND

GND

单独做lvs的时候都pass;-------〉那就是单个cell 没问题呗

整体的不对,出来什么错误呢?

ps:npoly和ppoly的gds no. 一样么?

layout上把两个GND连起来

找到问题了,

pad的版图里,GND net所在的二铝打了两个电阻标识,calibre认为这两个电阻标识把GNDnet 分成了三条。我现在处理的方法是把这个电阻删了。

不知道在runset file咋改这个规则?谁提点建议,大概是什么关键字什么描述语句处理这个问题的?

1. Device. 如果那里有两个device,两端自然不是同一根net,看lvs report就知道了

2. Connect. 如果connection的metal要求不含那个标识层,那你要让那里和旁边的metal connect起来才行

我对读这个runset file不熟悉啊,哪条指令控制让这样的metal连接起来的?

connect,比如说原来是:

connect M1_without_SAB diffusion by contact

你可以改成:

connect (M1_without_SAB or M1_with_SAB) diffusion by contact

也可以增加这句:

connect M1_without_SAB M1_with_SAB

对照你的 rule file, 不懂的查阅SVRF吧,完全不了解的话三言两语说不清

当然,首先要确保的是版图是正确的,还要知道 rule file 有没有提供 option 来控制(IFDEF 这种东西)

你很热心,都快赶上我年轻的时候了

晚上回去试试