为什么32nm工艺下温度对器件性能的影响跟45nm以上的相反呢?

哪个corner?TTcorneror SS corner?I remember both of them are similar

低温反型效益吧

虽然不太清楚是不是你想知道的,但我看过资料讲低温反型效应。在65nm下 ,延时最大的corner不是高温下的worst case 而是 低温下的 worst case low temperature。导致这种现象的直接原因是器件栅电压随着工艺进步也在下降。影响器件延时的两个因素:阈值电压和电子迁移率都是温度的函数,但是随着温度的变化,这两种参数却在相反的方向影响器件的延时。温度降低,电子迁移率升高,延时减小,而阈值电压升高,增大延时,反之亦然。在65nm以上,也就是高栅电压下,电子迁移率占主导,但到了低栅电压下,阈值电压就占了主导。所以低温下虽然电子迁移率有提高,但是阈值电压也太高了。

这个帖子的确算是长见识了

temperature inversion effect. 看foundary的工艺的特性, 这概念从90nm就开始讲了, 有些foundry 90nm就有这效应, 有些到45nm 才出现这效应. 该效应直接导致sign-off corner增多.

electron mobility is the dominant factor.

學到了 謝謝

确实长见识了!

这种低温反型效应,是由于在低温下粒子的杂质散射起主要作用。我们知道半导体中粒子的碰撞主要是以晶格散射和杂质散射的形式表现出来。在一定电压条件下,高温时,由于粒子的热运动速度快,导致迁移率降低;低温时,粒子运动速度变慢,迁移率会增大。

在工艺发展过程中,电源电压降低的同时阈值电压也在按比例缩小, 而管子的阈值电压主要是通过参杂的方式来调节的。当阈值电压减小,参杂的浓度升高,杂质散射就占据主导作用。杂质散射主要原理:低温时 粒子运动速度慢,受到邻近的参杂粒子的作用力的影响,减缓了粒子定向移动的速率(迁移率)。因而会出现低温时,器件性能降低的现象。仅个人观点,大家一起讨论啊

果断收藏!

长见识了!

学习了新知识。

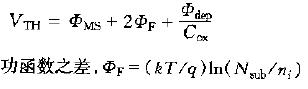

温度降低阈值电压不升高吗?

我看拉扎维书上写的

T增大Vth不增大么?

在一个设计中电压一般是固定的(非MSMV), 迁移率是同 (V-Vth)成正比的。这也是单元在SScorner下比FFcorner慢的原因。

虽然不太清楚是不是你想知道的,但我看过资料讲低温反型效应。在65nm下 ,延时最大的corner不是高温下的worst case 而是 低温下的 worst case low temperature。导致这种现象的直接原因是器件栅电压随着工艺进步也在下降。影响器件延时的两个因素:阈值电压和电子迁移率都是温度的函数,但是随着温度的变化,这两种参数却在相反的方向影响器件的延时。温度降低,电子迁移率升高,延时减小,而阈值电压升高,增大延时,反之亦然。在65nm以上,也就是高栅电压下,电子迁移率占主导,但到了低栅电压下,阈值电压就占了主导。所以低温下虽然电子迁移率有提高,但是阈值电压也太高了

=> 所以是說 65nm

mobility 低溫變好下..低溫速度比高溫快嗎?

但是到 45nm

mobility 影響不如 Vth ,高溫比低溫快.

但是如果是 0.18um or 0.35um process ?

一般都不是高溫是比較快嗎?

不太清楚那個對.高溫下電流不是都變大嗎?

涨见识,谢谢。