多个时钟CTS问题(encounter)

时间:10-02

整理:3721RD

点击:

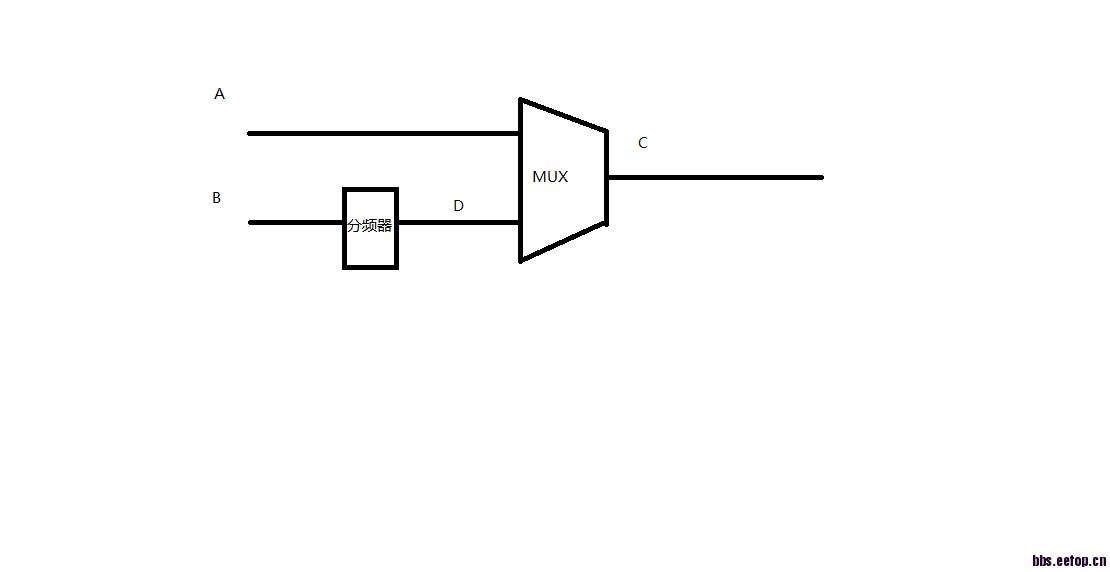

如图所示:

A点表示外部时钟iClk;B点表示内部时钟iClkSys;

D表示分频器产生的时钟iClkInter

CTS创建之后产生两个时钟--A,B;没有D

但是这样不能直接做CTS,因为工具会平衡AB之间的skew;

请问.ctstch文件改怎么修改,才能让时钟树更好的做出来?

还有sdc文件需要修改吗?

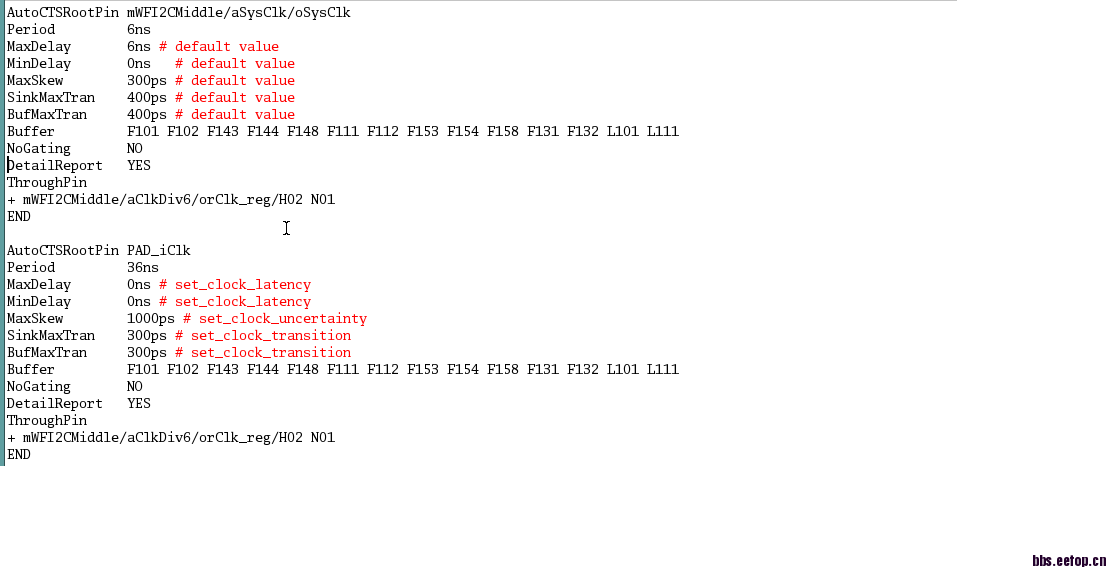

下图是.ctstch文件。分别对应时钟B和A

A点表示外部时钟iClk;B点表示内部时钟iClkSys;

D表示分频器产生的时钟iClkInter

CTS创建之后产生两个时钟--A,B;没有D

但是这样不能直接做CTS,因为工具会平衡AB之间的skew;

请问.ctstch文件改怎么修改,才能让时钟树更好的做出来?

还有sdc文件需要修改吗?

下图是.ctstch文件。分别对应时钟B和A

现在的目标是啥?

注意几点:

1)clock缺省不能穿过flop ,除非是generated clock

2)除非是clkGroup里面, 否则不会自动balance each clock

3) mux,icg不会挡住clock穿过,

4)有必要修改cts spec, 可以一个一个做,如果觉得一起做多个不好控制的话,

目标是把时钟树做的好点,这种状态下插入的buffer级数很大,且Post_CTSOptimization 后还会有2000多个violation。

A,B不是一个source时,时钟不会自动平衡啊,A,B两点怎么会balance呢?

在C点作为rootpin做cts试试呢

是的,但是encounter会认为他们是同一个,会把它们尽量平衡起来,于是就出现问题了

那样的话CTS综合时候停不下来了

为什么会停不下来?规模很大么?还是除了MUX还有别的东西?网表没问题?

整个时钟树的情况如何,有没有其它的东西你不知道的,有没设定到的地方,导致不能完成?

EDI的时钟树还是比较好设定的,只要你了解清楚结构。一般没啥问题的

这话说到点上了,

"了解清楚结构"!

答案呢....期待...

没后续吗