formality在match和verify的时候出现的错误都是在电源地上

时间:10-02

整理:3721RD

点击:

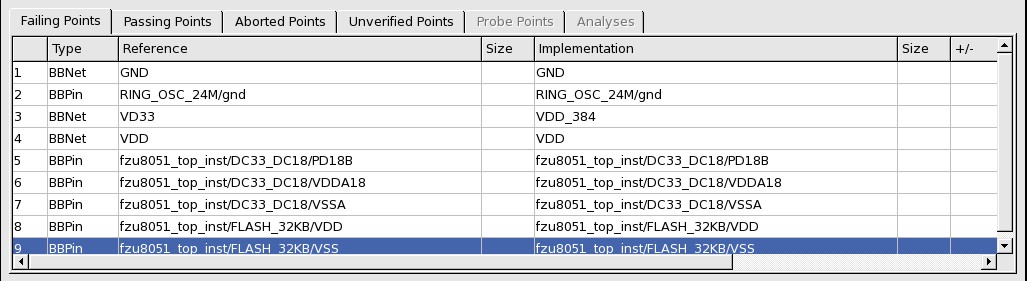

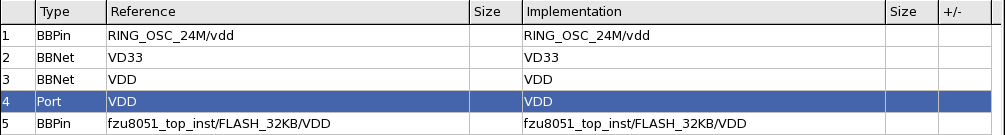

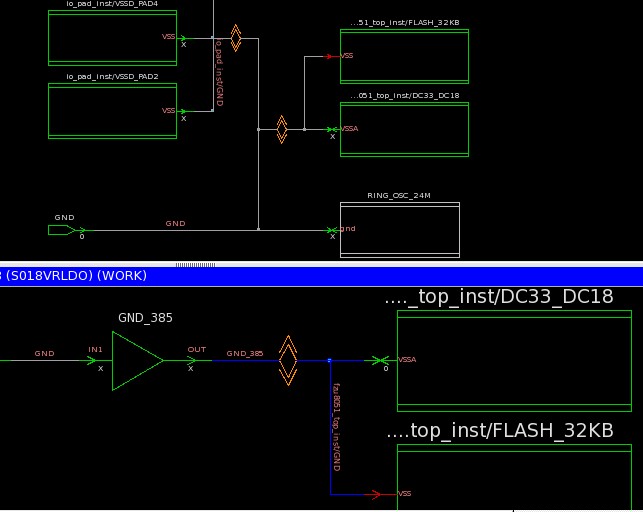

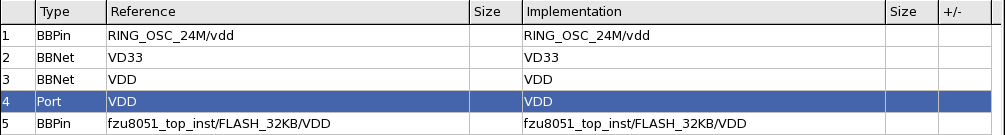

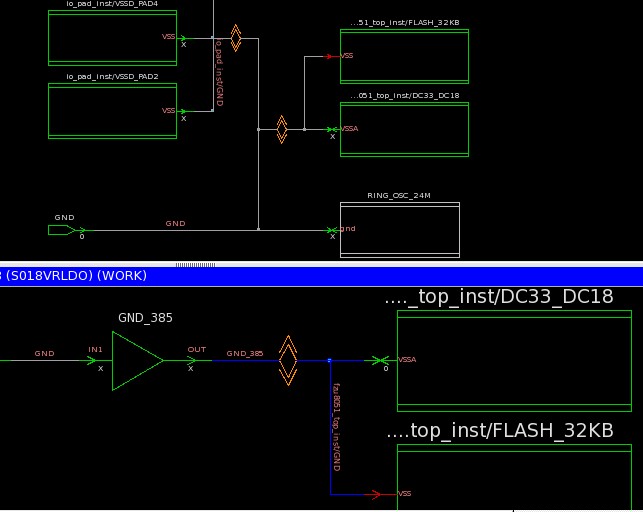

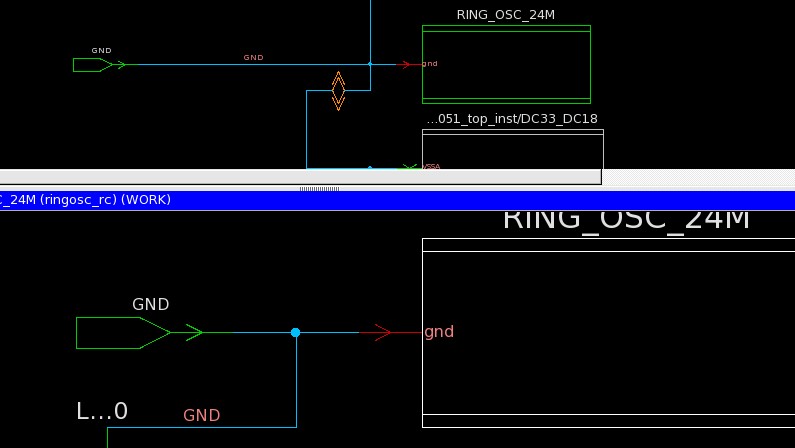

formality在match和verify的时候出现的错误都是在宏模块的电源地上,看来下图,一般综合完后的网表不匹配的电源地会加上buff或者接逻辑1或0,核对了一下两边的网表,基本上都是相同的,没有什么不一样。以为是DC的时候宏模块和电源模块没设置don't touch,后来从新综合了一下,出现的问题还是一样的,有没有人碰到这个问题呢?是哪里出现问题了?

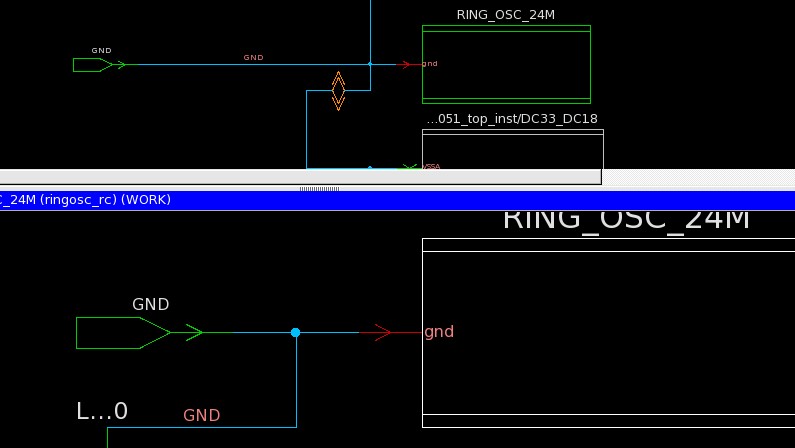

之前综合的时候将dont_touch设置在整个宏模块上面,出现了错误。之后我将宏模块上面出现问题的pin也设置为dont_touch_network了,但是为什么有的可以设置成功(设置成功的pin后面的不匹配问题就没了),有的不行(我从图中看net的属性是undefined),手动改成true,在生成网表依然不行,这是为什么呢?

dont_touch_network其实不能对net进行设置,对pin设置好像对net不起作用,。现在我用set_dont_touch [get_nets GND] true对电源地网络进行设置,以防他优化,可以后来发现GND的问题没了,可是对VDD做同样设置,结果VDD问题还一直存在,现在问题出现在port(之前是在net和pin上)上,如果在port上要怎么解决呢,貌似命令不对port起作用。