请问 SoC encounter 产生自定义的 Macro 时PowerRing怎么加?

在单独生成subdesign的版图后,用saveModel把它保存为LEF,然后重新再在encounter里面以macro的方式调用到Topdesign。

以上就是我产生Macro的方法。(请问这样做正确吧?)

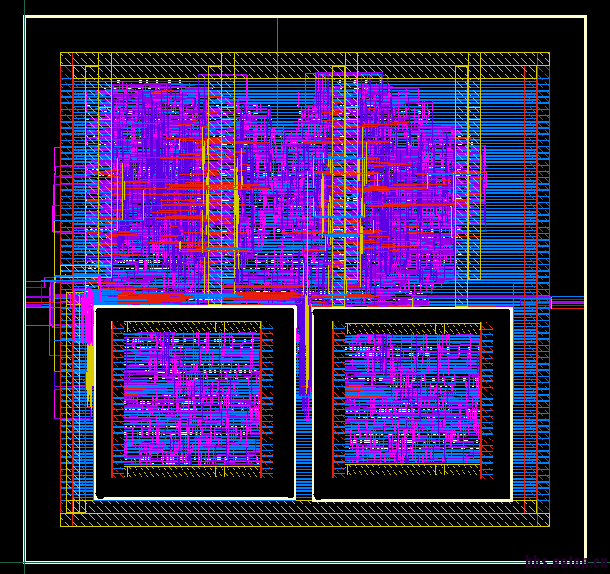

但是我发现,如果按照普通设计方法对subdesign布局布线的话,subdesign 的版图就会有一圈明显的 power ring和 core margin,这样的话,放到Topdesign中,再用virtuoso显示就会如下图所示,露出一圈难看的黑窟窿。

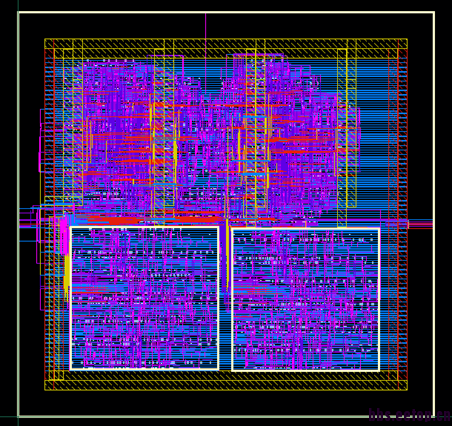

但是如果我在对subdesign布局布线时,不加power ring的话, 而且 core margin 设成零, 那么就不会有这种黑窟窿,如下图所示:

信号连线,我已经查过,都是连接正确的。但是问题是,我对于VDD和VSS没有信心,总担心这样没连上 Power。

请问一般大侠们生成自己的macro的时候,是怎么处理以上问题的? Power连线怎么办?

与RAM一样,你如果看到有power连线,那就是连上了

多谢小编回复。

我想借此问一下关于global net connection,还有 vdd/vss IO 这种一系列关于power的问题。

一般的SoC encounter 实验手册,对于VDD和VSS都是如下处理,如果不涉及IO 很多压根不涉及global net connection。

最基本的从Design Import ---> Advanced----> 选 Power,可以看到已经有一对默认的 net(s) 比如 vdd vss。

不要求实验者修改,而且以后 vdd vss 会自动出现在 Add Rings 或者 Add stripes 之中,一直不用管设置,一路鼠标就完成整个Layout了。

以上这种实验没有涉及到 global net connection。

如果需要加 IO 和 pad,就得用 global net connection了吧。

首先,目前的netlist verilog 中的所有门级cell 还都没有 VDD 和 VSS 这两个port。

有一个命令可以把目前的netlist存成有带有VDD和VSS的verilog代码,不知道这一步骤是否必须?

vss/vdd 对应的IO cell 必须出现在verilog代码里,对吗?

然后,pad 都是在 .io 文件里分配的,对吗?

还查到,需要connect ring pins, 这个我以前没有用过。应该是版图中产生Pad与power ring物理金属连线的一步吧?

有感觉 global net connection 本质是在声明 pad 或者 pin,那样的话就不用 .io 文件里声明Pad_VDD了吧?

我对于这一块儿理解比较混乱,请小编和大侠们点拨。