菜鸟求助 area report 与网表不符怎么回事

时间:10-02

整理:3721RD

点击:

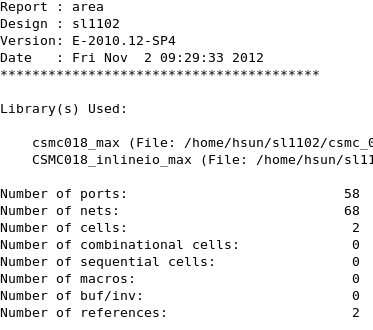

各位大神有没有遇到过这个情况

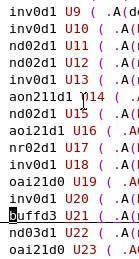

虽然area report上很多是0但网表里都是有单元的

工具是synopsys的dc

坐等

都能和库对应上的

貌似只是一些cell数量在report的时候显示不出来

虽然area report上很多是0但网表里都是有单元的

工具是synopsys的dc

坐等

还没有综合到gate level

是compile命令完成以后才生成报告的已经综合出来门级网表了只是报告里的一些单元为0和网表里的不相符

compile命令完成不等于中间的步骤没有错误,先检查link是否正确,不能有error和warning

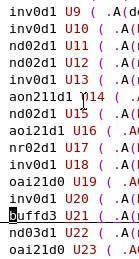

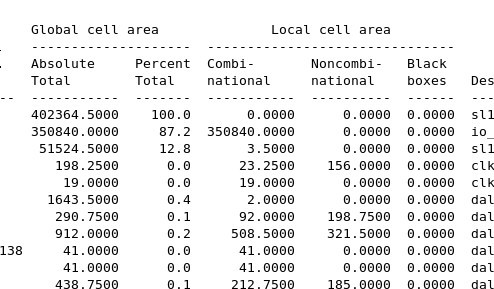

生成的门级网表和各个模块的面积报告我都查了

都能和库对应上的

貌似只是一些cell数量在report的时候显示不出来

没有error和warning

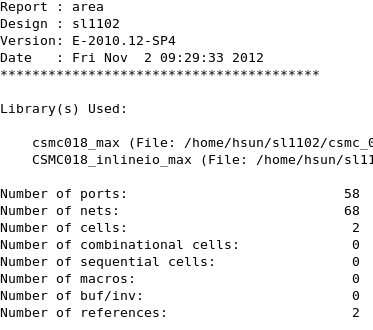

1楼和5楼截图不像是同一个block

注意1楼截图的最后一行

是一个design报告的综合完成以后一楼的是直接report_area的五楼第一个图是report_area -hierarchy 出来的

第二个图是write_file -format verilog -hierarchy -output *.v 出来的用这个门级的.v文件是可以通过仿真的

那个number of references 是什么东西?是库里的标准单元?

难道1楼只是top level的?

小编大人这么一说貌似有点像我去查查看

它报的就是顶层多谢小编

小编很强大,

小编太强了