时钟的定义

时间:10-02

整理:3721RD

点击:

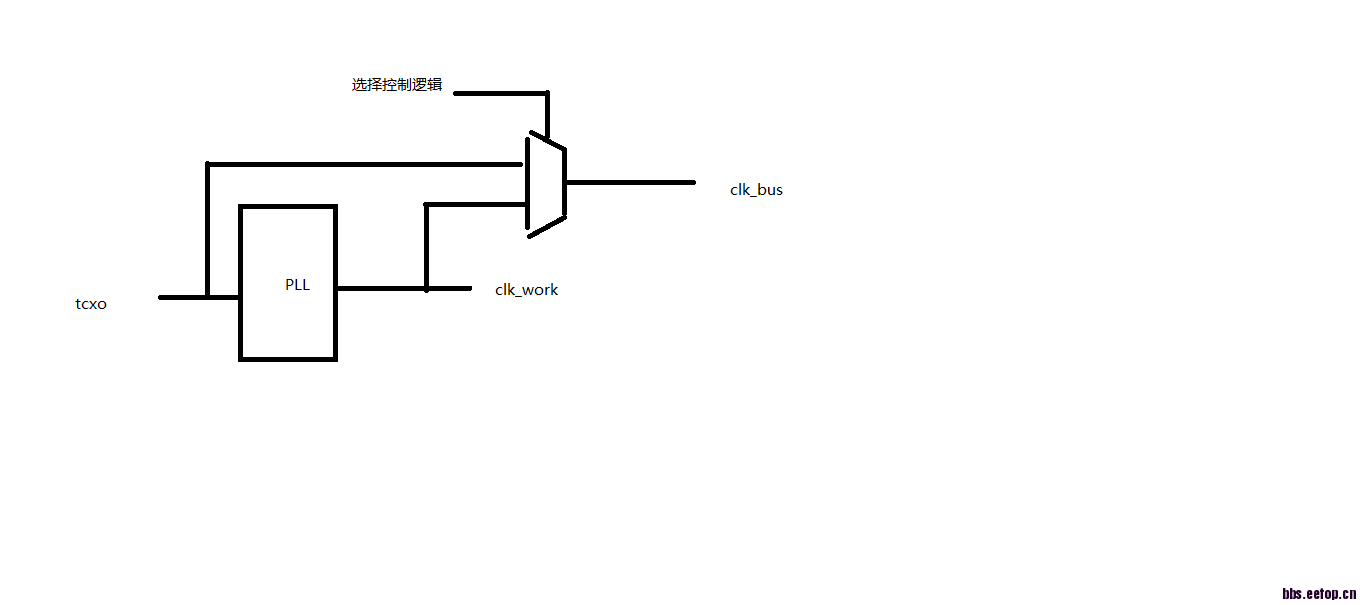

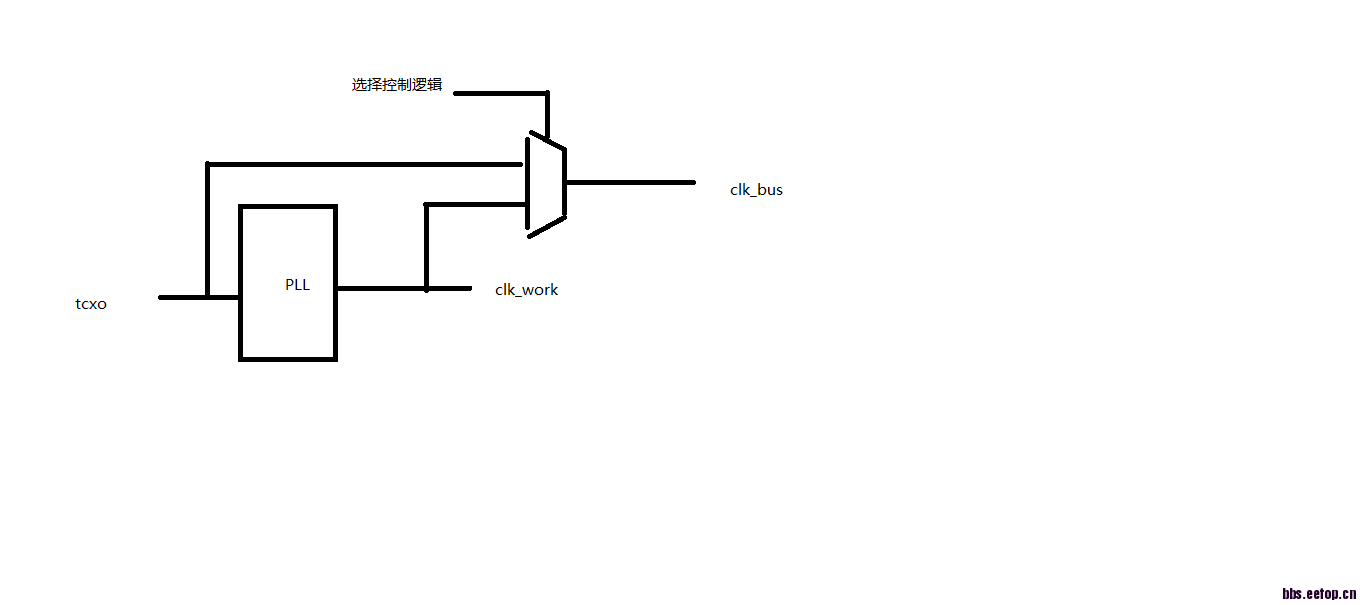

PLL出来的时钟即做了总线时钟(clk_bus),又做了工作时钟(clk_work)。如下图所示。

Normal模式下,clk_bus直通PLL出来的时钟,非tcxo晶振时钟。

这种情况下,该如何创建时钟?

有两个假设条件:

1.两个时钟之间没有数据交付

2.有数据交付

上述两个假设是不是会导致时钟定义完全不一样?

Normal模式下,clk_bus直通PLL出来的时钟,非tcxo晶振时钟。

这种情况下,该如何创建时钟?

有两个假设条件:

1.两个时钟之间没有数据交付

2.有数据交付

上述两个假设是不是会导致时钟定义完全不一样?

是的。

1.没有数据交互:你可以在PLL后和mux后各create_clock一个时钟。

2.有数据交互:你可以在PLL后用create_clock生成一个时钟clk_work,然后在PLL之前create_clock再定义一个时钟clk_ref,最后设置timing_enbale_multiple_clocks_per_reg为true。因为clk_ref和clk_work的时钟相位关系不确定,一般还要用set_false_path或者set_clock_group设置2个时钟之间的path为异步path。

这种设置方法有个必须要注意的地方,就是你的RTL必须保证当clk_bus选为clk_ref时,clk_bus和clk_work之间没有数据通路或是做了同步处理!

以上所说的前提都是clk_ref和clk_work没有相位关系,如果有相位关系的话就有另外一种比较简单得设法了。

只要晶振频率小于PLL输出频率,无论是否有数据交换,只定义一个clock在PLL的出口,MUX控制选择PLL

在后端,根据设计的需要,可能要de-skew晶振时钟和PLL输出时钟

请教陈小编:

如果需要de-skew的话,需要如何处理呢?