CTS与timing check

时间:10-02

整理:3721RD

点击:

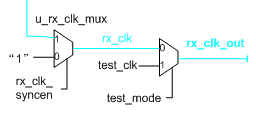

最近遇到遇到一个很奇怪的问题,网表相同,SDC相同,只有做CTS的方法不同。如下图

第一个MUX是gating结构,我将产生rx_clk_syncen这个是能信号的DFF(rx_clk_syncen_reg)的CK端设成了ignore pin。希望在CTS的时候不对这个DFF进行平衡。

SDC里面对第一个MUX之前的时钟定义为core_clk,对第二个MUX之后的时钟定义为generate_clock,名字是rx_clk_out.

然后再check timing的时候,没有ignore的情况下:后面的DFF是在core_clk的时钟域里。当我ignore之后,就认为是在rx_clk_out的时钟域里。

而且core_clk 和 rx_clk_out频率还不一样。

我一直觉得,CTS的过程本身不会影响到check timing的方法。求大神们帮忙看一下。

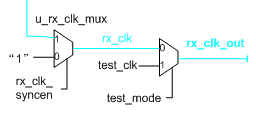

第一个MUX是gating结构,我将产生rx_clk_syncen这个是能信号的DFF(rx_clk_syncen_reg)的CK端设成了ignore pin。希望在CTS的时候不对这个DFF进行平衡。

SDC里面对第一个MUX之前的时钟定义为core_clk,对第二个MUX之后的时钟定义为generate_clock,名字是rx_clk_out.

然后再check timing的时候,没有ignore的情况下:后面的DFF是在core_clk的时钟域里。当我ignore之后,就认为是在rx_clk_out的时钟域里。

而且core_clk 和 rx_clk_out频率还不一样。

我一直觉得,CTS的过程本身不会影响到check timing的方法。求大神们帮忙看一下。

什么工具?

找到原因了,和工具没关系,我们这边坐CTS的时候始终的名字弄错了,没做上树......

低级错误啊,浪费了整个一晚上的时间。