tetramax产生测试向量的问题,各位大牛帮帮忙

原本的test_mode端口不打算封装出来,复用了analog模块SCAN_IN端口出来的一个信号,经过相关电路,得到的信号TESTMODE,进入测试模式;

大概是这样的,起先在顶层vabt端口为1,然后在顶层的rest端口灌入一个下降沿,再从vabt端口连续灌入16个下降沿,最后vabt恒为0,进入测试模式。

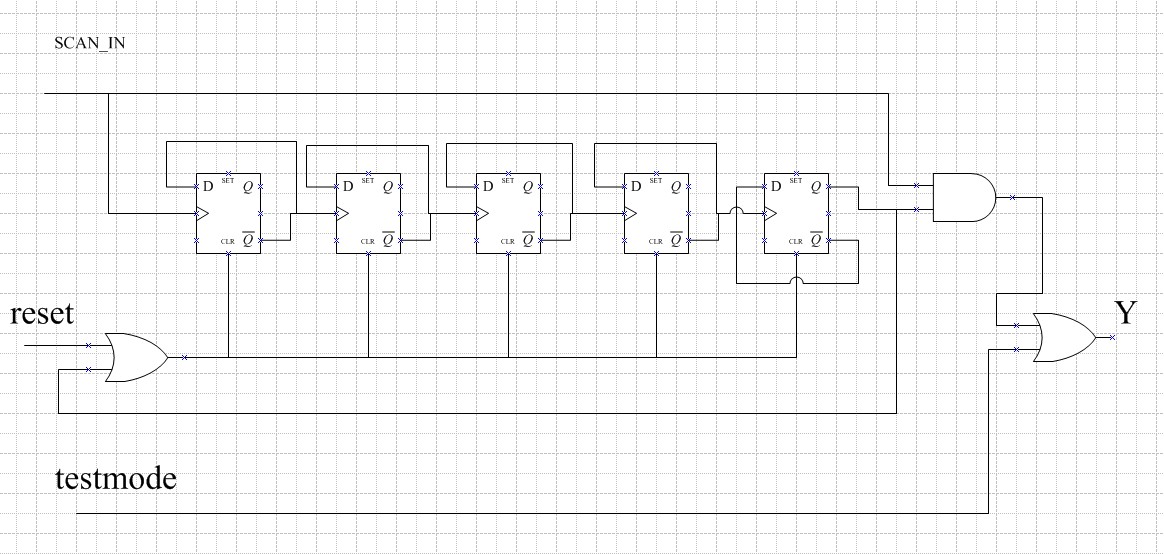

SCAN_IN端口出来的信号,经过pad module一些相关电路,该电路由5个移位寄存器组成,SCAN_IN信号作为第一个寄存器时钟,然后信号从最后一个寄存器的Q端出来,这个信号代替原来的testmode作为测试信号,analog 模块在测试的时候功能上等效于一个反相器,产生向量的时候,在网表中可以用一个inv代替。关键的问题是:我要怎么样在spf中定义才能合理的进入测试模式呢?

各位大牛帮忙出下主意,谢谢了!

画个图吧,图是工程师最直接的语言

如何改spf,实在麻烦

朋友,给点意见啦

scan_in 不允许跟test_mode复用,这两个在测试模式都要用到的引脚,复用只能开启其中一个,所以你说的没法办到。你可以跟其他的功能pad复用

testmode是顶层的一个端口,但是现在不打算封装出去了,现在要SCAN_IN经过上面的电路产生一个信号做测试模式信号

重点是SPF中我要怎么描述,才能得到正确的激励?

scan_in是扫描输入,怎么可能做到产生测试模式信号,据我所知,做不到。,你随便再找一个普通的端口,复用一下不久行了。

SCAN_IN不是扫描输入端口啊,是模拟模块产生的一个信号

是不是我问题描述不清楚了,现在的问题是,要怎么样在spf中描述,产生测试模式信号?测试方案设计前端已经设计好了 ,现在就是spf的问题,如何在test_setup中描述进入测试模式

就算是在test_setup文件中,也应该是对输入端口进行Pi的啊。那这个时候就得定义你的这个产生测试模式信号可由哪个外面输入控制。试下将那个控制端口设置能产生你需要测试模式的值。如果你的这个模拟ip产生的测试模式信号压根就不受外面控制,个人觉得这个时候很难通过改spf来实现啊。

顶层的vabt端口可以直接控制SCAN_IN信号,设计上可以保证,先不管如何设计,现在就是要如何在spf中表示这些激励信号:

首先,rest先复位,vabt为1。

然后,vabt连续灌入16个低电平。

最后,vabt保持为0。

这样就可以得到一个测试模式信号。问题就是这些激励信号怎么在spf中描述出来呢?

test_setup中好像有个force的吧,可以描述这个激励的吧。

add pi constraints

V {

"SCAN_IN" = 1;

}

在测试协议的最后test_setup部分 v{}里面,添上去就可以了。

Add pi constraint 是否比较难描述这种不是很有规律的信号,还是在test_setup中用V基于clock来描述比较容易点。

试了很久,最后在test_setup这样设置,定义3组测试周期

V {rest = P ; vabt=1;}

Loop 16 V { V{rest = 1; vabt=0;}

V{rest =1 ;vabt =1;}

}

V {vabt = 0;

scan_clock =0;

rest=1 ;

}

这样就可以了

感谢各位的回帖

不知道还有没有其他的写法,这样大概3500ns之后进入测试状态,

要是在顶层直接有testmode信号的话,200ns就进入测试状态了