PARA-075 (error) Could not resolve net '%s'.

时间:10-02

整理:3721RD

点击:

做PT的时候,用starRC提取的spef文件反标注到STA中,发现有些线网不能resolved,提示错误如下所示:

Error: Could not resolve net 'DECODE/Y_last[3]'. PARA-075

Error: Could not resolve net 'DECODE/Y_last[1]'. PARA-075

(似乎这些net连接的pin在logical design中悬空)

查了以,说是physical design 与logical design不相匹配,我不知道这个问题到底出在哪里?麻烦各位知情者帮忙解答!

Error: Could not resolve net 'DECODE/Y_last[3]'. PARA-075

Error: Could not resolve net 'DECODE/Y_last[1]'. PARA-075

(似乎这些net连接的pin在logical design中悬空)

查了以,说是physical design 与logical design不相匹配,我不知道这个问题到底出在哪里?麻烦各位知情者帮忙解答!

有没有人知道啊!?

同求解!

我以前遇到过类似的错误,原因是starRC抽取spef时(对于MILKYWAY_DATABASE),net的名字和ICC write_verilog的net名字不一致,解决方法是在在ICC里执行

change_names -rules verilog -hierarchy -verbose

不知道你具体用的啥工具

谢谢你的答复,我做PR用的是Astro,没有用ICC,不知道在Astro中用什么命令,才能解决这个问题呢?

Astro没怎么用过,应该有类似的命令吧,具体我也不清楚

不行的话,在write_verilog时多加一个-wire_declaration的参数,重新写一个带wire的netlist试试

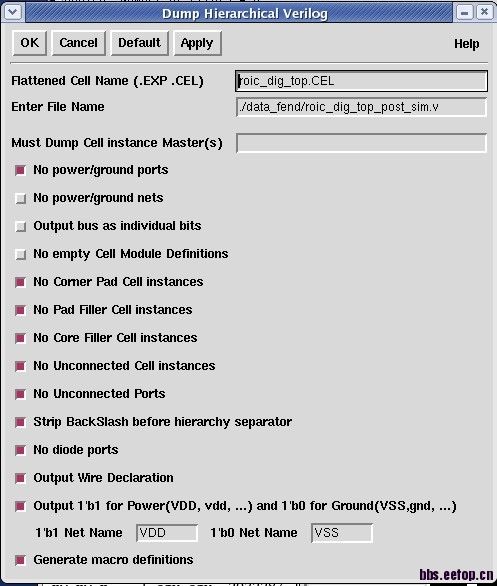

用ASTRO在导出netlist for post layout simulation 的时候不要选no empty cell module definitions 这个选项。

这样导出来的网表有标准单元的module定义。

cell > hierarchical verilog out

嗯!试过了,就是这个原因,成功解决了,谢谢!