STA clock穿越reg问题

时间:10-02

整理:3721RD

点击:

遇到这么个问题,用ETS作时序检查。

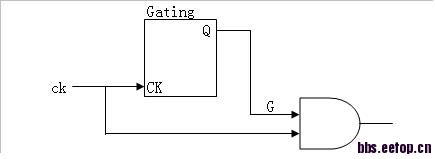

这样一个简单的电路:

时钟ck到一个叫Gating的reg,打出一个gating信号G,然后G与ck走到一个gating cell(一个简单的与门)

在生成的时序报告中,信号G也被ETS认为是时钟ck的path,也就是说ck穿越reg到G,再到gating cell输出也认为是时钟ck的一条路径进行timing分析,并且因为G被认为是ck的一个path,所以G不被认为是gating信号,那个gating cell也不进行clock gating检查

如何让工具不穿越寄存器?

请指教,谢谢

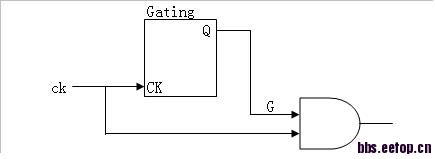

这样一个简单的电路:

时钟ck到一个叫Gating的reg,打出一个gating信号G,然后G与ck走到一个gating cell(一个简单的与门)

在生成的时序报告中,信号G也被ETS认为是时钟ck的path,也就是说ck穿越reg到G,再到gating cell输出也认为是时钟ck的一条路径进行timing分析,并且因为G被认为是ck的一个path,所以G不被认为是gating信号,那个gating cell也不进行clock gating检查

如何让工具不穿越寄存器?

请指教,谢谢

你这个 gating cell是icg 还是 latch, 如果是icg, clk肯定穿过啊,是必然的

是latch,就会停下

建议用icg吧,别用离散的gating cell,

实在ets不认这种gating,你就用set_clock_gating_check -setup -hold [get_pins XXX ]

显式的指出就好了,

在and gate 的输出端generate clock了吧?没有generateclock的话按道理不会认为Q端也是clock的啊,若是有generateclock,直接把这个generate clock去掉好了。

set_disable_timing -from G -to Q [get_cell u_latch]