用PT进行STA时生成sdf时出现setup和hold的和为负是怎么回事

想与大家讨论一下!

你是说SDF里面的setup/hold为负数?

我之前也遇到过,只是一个warning,我也没有太仔细研究他,不知道能否忽略啊。

是在STA过程中的log文件中的setup和hold之和为负的warning。

我开始以为是sdf的版本的原因,但是使用生成sdf3.0,还是有这个原因。不知道能不能忽略。不知道楼上怎么处理这个问题!

与大家探讨下!

没看懂

“setup和hold之和为负”

改天我将warning报告粘出来吧!

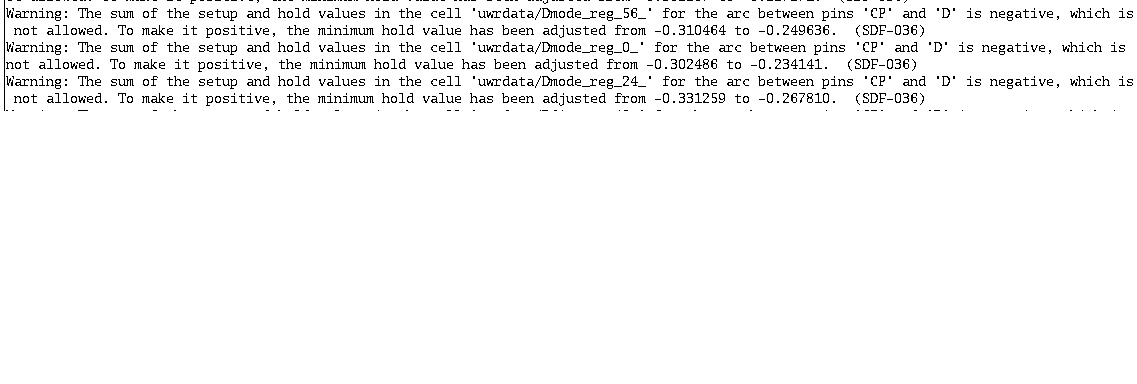

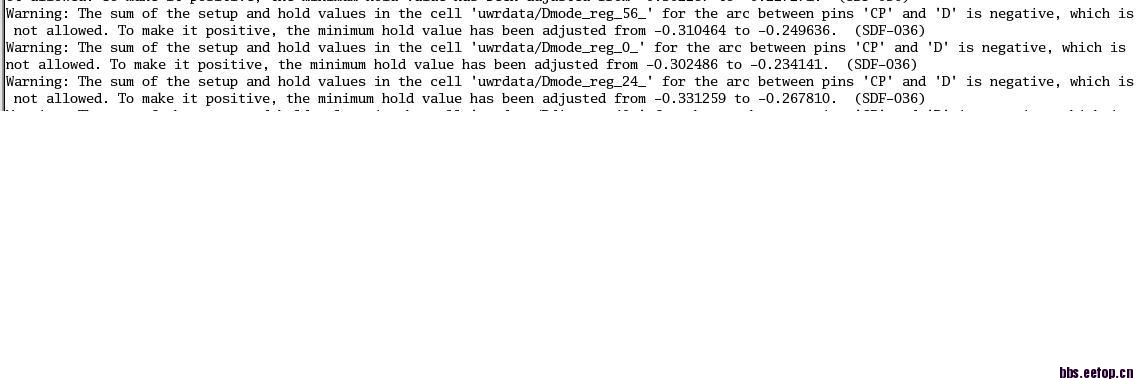

附上警告报告图,希望大家帮忙分析分析!

抱歉,不清晰,再传一次。

不需要处理,因为实际情况SETUP 和HOLD都不能为负,所以和不能为负,但是做STA时有些库里面根据查找表可以得到负的值。

关于这个warning,PT是怎么解释的,对于某个timing arc,它的setup或者hold可以为负(你没有看错,可以为负,而且实际上这样的时序逻辑是存在的),但是2数相加一定要大于0

你要做的是检查SDF的生成过程,看看是否在某个设定上不合理

是的,关于这个解释,PT是定义的,CP到D的timing arc上的setup和hold之和为负。这是这里报错的主要地方。这离的warning全部是对寄存器,也就是说实际上的寄存器的setup和hold之和不应该为负的,但是它的setup或者hold可以为负,这也是可以理解的。

现在关键是也不知道这个问题出现的原因是时序库的原因还是design的原因?

如果是design的原因,这好像提示也不是很多啊!

能有人解答!

10楼里已经有建议了!

不用太care的,负沿时即使写出来了,在仿真时大多没有使用(直接用0替代了),如果sdf里面不想写负沿时出来可以试试加上 -no_negative_delays,这样在写sdf时负数会直接用0替换。

如果负沿时用0替代,这样的话后仿时出现violation的时间窗口就更大了,比实际情况要严格,所以仿真没问题的话应该是没有问题的。

另外,新版本的仿真工具在这方面已经在改进了,可能已经能够对负沿时进行处理了,这个可以查查工具手册。

谢谢楼上的解释,只是想知道是什么原因,应该是库的原因吧。

谢谢分享

对于某个timing arc,它的setup或者hold可以为负,这是为什么呢?