MOS器件中孔到poly的距离不一样怎么解决?

时间:10-02

整理:3721RD

点击:

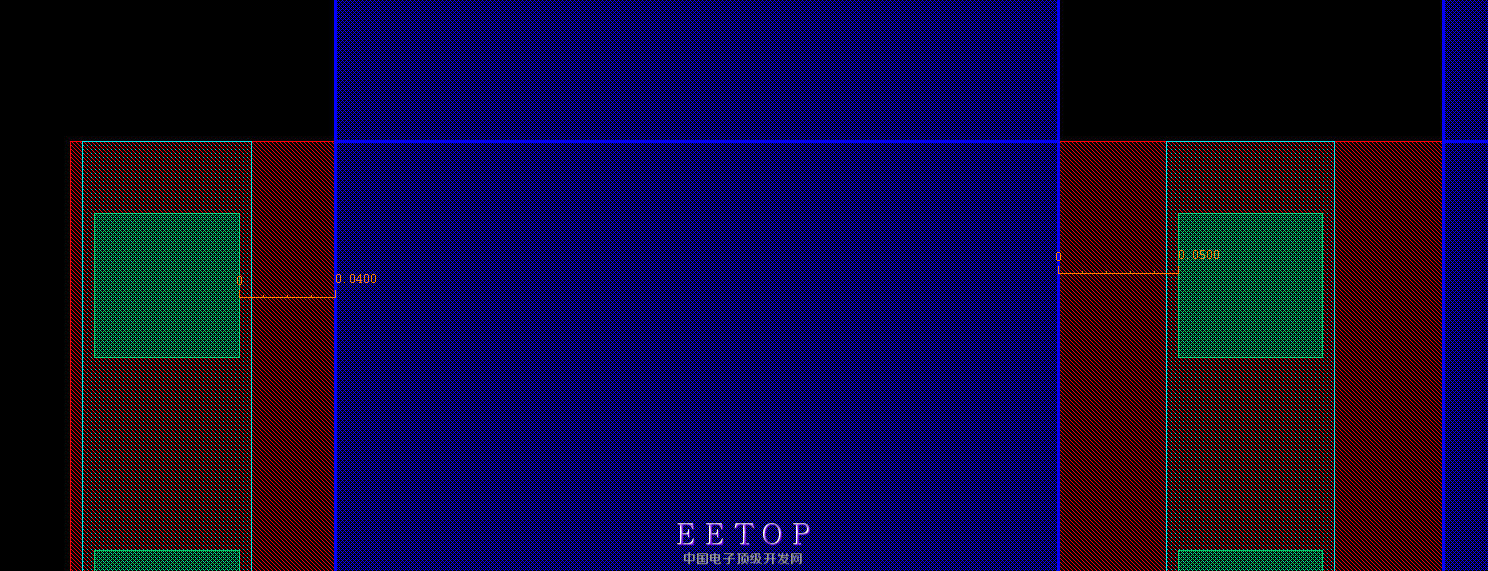

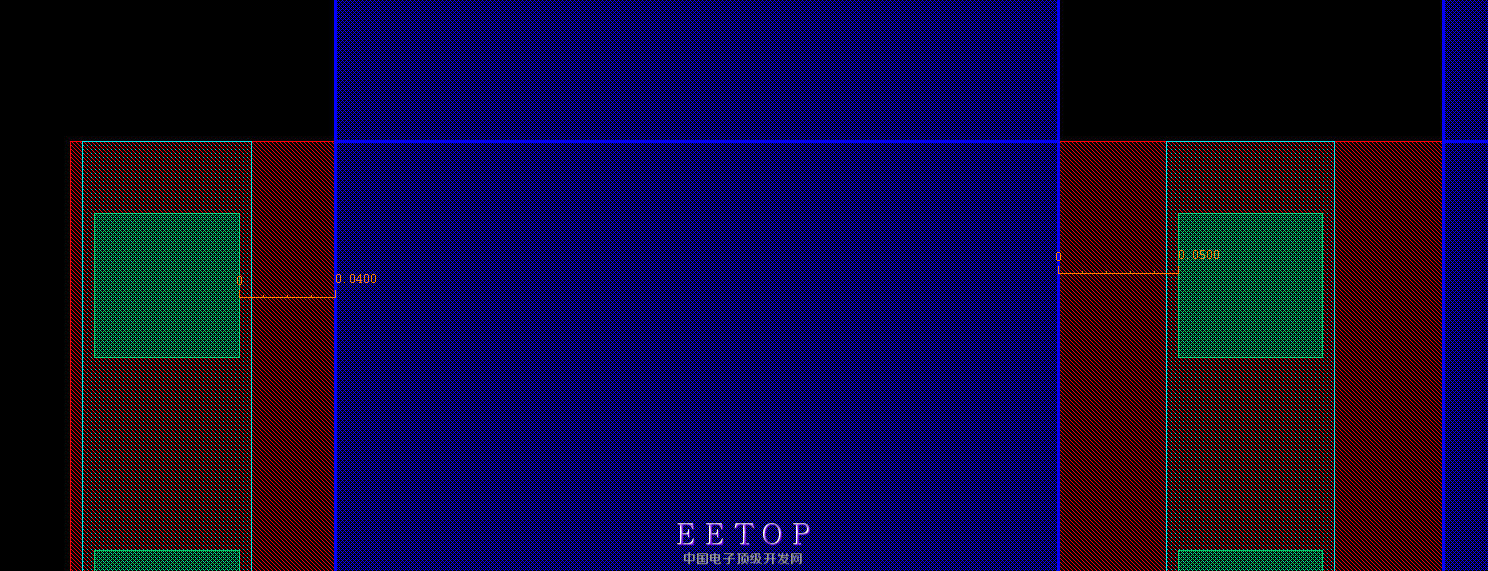

从PDK库中调出的MOS在两个及以上的时候,MOS器件两边的孔到poly的距离跟里边孔到poly的距离不一样,这是怎么造成的?有什么方法可以改掉这个问题?

应该是PDK写得有问题,建议反馈给fab。

或者会不会是grid点的问题,如果你的grid是0.01,而MOS length是0.01的奇数倍,比如说0.41,若果0.41被当做path线处理,那为了保证不off grid,中线会向某一边偏0.005,也就是说一边是0.2,一边是0.21,结果就不再是对称的了。不过这只是我个人猜想。

看你旁边还有一个mos,是不是两个mos吸附到一起之后成这样的,单个应该没问题,这个是pcell没有做好

应该是fab的PDK做成这样了边上的孔到poly距离是0.04,里边的是0.05,以后只能麻烦点直接改MOS的finger了

这个MOS的finger是大于2 的,所以不是被吸引产生的错误,如果MOS的finger为1,D/S两端孔到poly的距离全都是0.04

这句是一个MOS,它的finger大于2~应该是PDK的问题吧

pdk问题,妥妥的

你看看PDK给里面有没有设置孔到GT间距的参数!不然就自己做PCELL

楼上说的对,有些PDK确实存在源漏到栅间距的参数,你看看你的PDK是否存在

做PDK里pcell的人没有格点化处理。

这么小的CTtoGate,HL的pdk吗?

这是40nm工艺的pdk

40n 基本能确定是由于gate 距离导致的,pdk 没问题。是使用习惯的问题而已,人性化一点的pdk 带有外边ct 到 geta 距离的选项 非要一致调一下就可以了。

就是40nm的PDK出这种错误,想知道是HL的还是S的。T应该不会吧。