在virtuoso中不能打孔

工艺库没有contacts/vias,检查下工艺库是否完整。

有可能是 tech file 裡 沒有定義

看下*.tf文件有没有对symContactDevice的定义,如果没有就调不了。

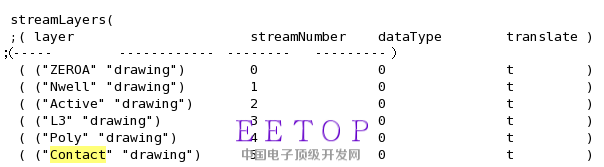

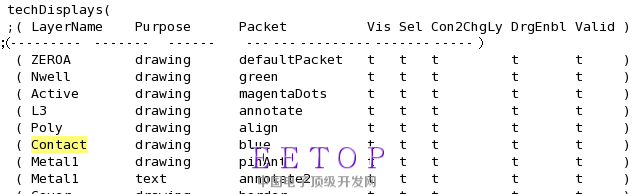

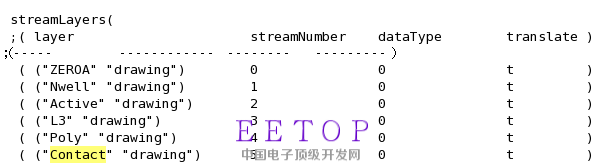

是这个吗?我看不懂工艺文件。

是这个吗?

你截取的文件图里面的contact是drawing,不是孔cell,所以这个你是没有办法O出来的,你只能在文件库中存在孔cell的情况下,你才能O出来,孔cell里面包含contact(drawing)和M1最小包孔还有active或者POLY最小包孔,V1、V2。都是同样的问题,希望对你有用

谢谢,我已找到一个完整的工艺库,这个问题已经解决了,但是我还有一个问题,我调用出来的孔在做DRC时报错,比如说minimum MT1<0.81,我以前都是用的laker画,调用出来直接可以用,现在用virtuoso调用出来还要改大小,这是软件不同造成的,还是说我的操作有错误?本人小白一个,又是自学版图,如果问的问题太渣,还请不要见怪!谢谢你!

你这个问题是不是这样的,我猜想你是不是只调用了一个单个的孔,然后run的DRC,这样的话肯定是过不了DRC的,根据你的DRC结果判断,应该是MT1最小面积0.81,也就是做你的MT1最小要0.9X0.9,这样才不会出现DRC,你的单个孔的MT1只保证了最小包孔,但是不可能满足最小面积,所以你在画版图放孔时候上面放的MT1最小面积是0.81,跟孔单元没有关系了,孔单元内部的MT1只是单单满足了包孔要求,希望你能看明白,if you have any question, please reply me,thanks

跟你说明一下,我没有办法回复你的短消息,你可以跟帖,我就可以回复你了,不然我没有办法回复你,thanks

比較像這個

symContactDevice(

; (name viaLayer viaPurpose layer1 purpose1 layer2 purpose2

;w l (row column xPitch yPitch xBias yBias) encByLayer1 encByLayer2

legalRegion)

(M1_Poly Contact drawing Poly drawing Met1 drawing

0.22 0.22 (1 1 0.47 0.47 center center) 0.10 0.06 _NA_)

(M1_Nwell Contact drawing Nisland drawing (Nselect drawing 0.02) Met1

drawing (Nwell drawing 0.53)

0.22 0.22 (1 1 0.47 0.47 center center) 0.10 0.06 _NA_)

(M1_Psub Contact drawing Pisland drawing (Pselect drawing 0.02) Met1 drawing

0.22 0.22 (1 1 0.47 0.47 center center) 0.10 0.06 _NA_)

(M2_M1 Via1 drawing Met1 drawing Met2 drawing

0.26 0.26 (1 1 0.52 0.52 center center) 0.06 0.06 _NA_)

(M2_M1_3x3 Via1 drawing Met1 drawing Met2 drawing

0.26 0.26 (1 1 0.82 0.82 center center) 0.06 0.06 _NA_)

(M3_M2 Via2 drawing Met2 drawing Met3 drawing

0.26 0.26 (1 1 0.52 0.52 center center) 0.06 0.06 _NA_)

(M3_M2_3x3 Via2 drawing Met2 drawing Met3 drawing

0.26 0.26 (1 1 0.82 0.82 center center) 0.06 0.06 _NA_)

(M4T_M3 Via3top drawing Met3 drawing Met4top drawing

0.36 0.36 (1 1 0.71 0.71 center center) 0.06 0.3_NA_)

(M4T_M3_3x3 Via3top drawing Met3 drawing Met4top drawing

0.36 0.36 (1 1 0.82 0.82 center center) 0.06 0.3_NA_)

)

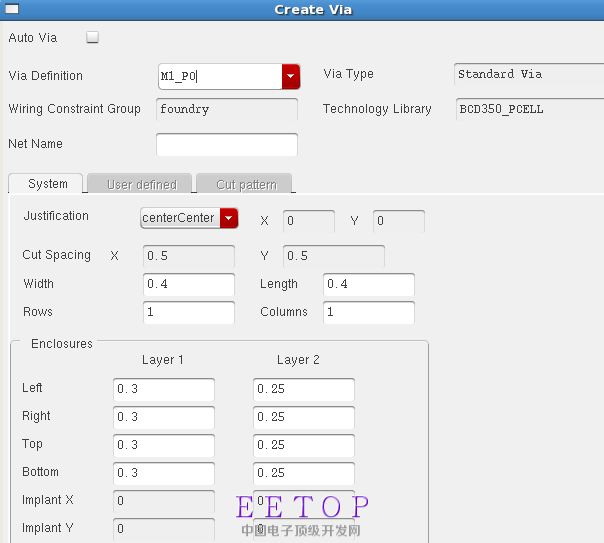

谢谢,你讲的很详细,确实如你所说,我还想问一下,能不能将孔设置成我想要的尺寸,保存下来,要不然每次调用改一遍感觉挺麻烦。这是我O键出来的对话框

首先确定一下,你这应该是615版本的,这个版本还想保存不了自己设定的值,但是还有一个办法,就是你的孔CELL所在的库你是否有编辑权,如果有你可以修改孔cell的包孔,简单地说就是直接把基本库中的孔cell编辑一下达到你想要的效果,不知你是否能明白,如果不明白可以再问我

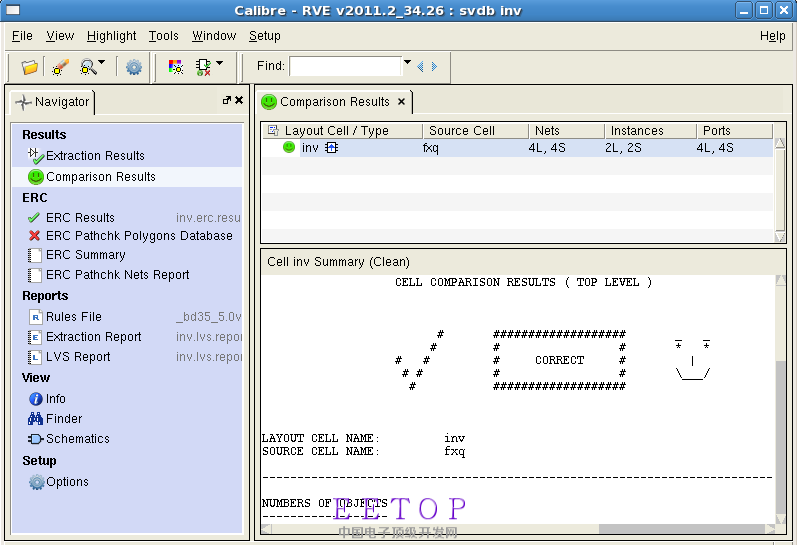

好的,谢谢,我明白了,还有两个问题要请教,一是我做LVS验证通过了,但是有这个ERC错误,这个是什么原因,可以忽略吗?因为它的ERC Results 是通过的,如果不能忽略,要怎么解决呢?

先回复你第一个问题,ERC(extraction rule check)

看到你的extraction results是通过的,所以你的ERC是不用关心的, 一般ERC有问题,会在这一项里面出现错误

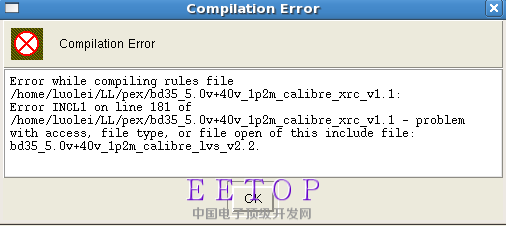

第二个问题,先看他报出来的ERR,是说你的RES2没有定义,所以无法提取,也就是规则文件错误了

另外你可以点击一下不通过的那个ERC看一下他是什么情况,如果可以修,你就修掉就完事了

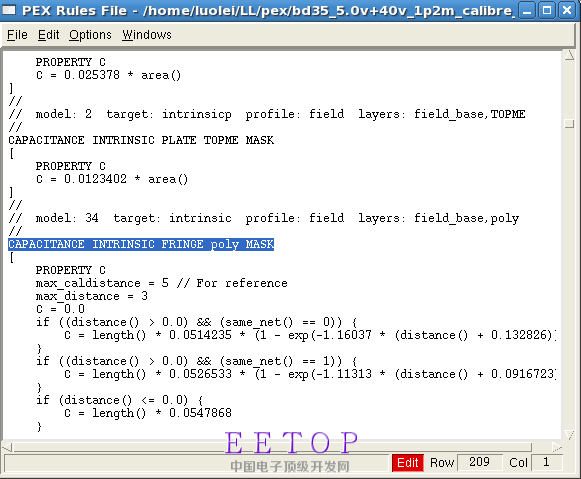

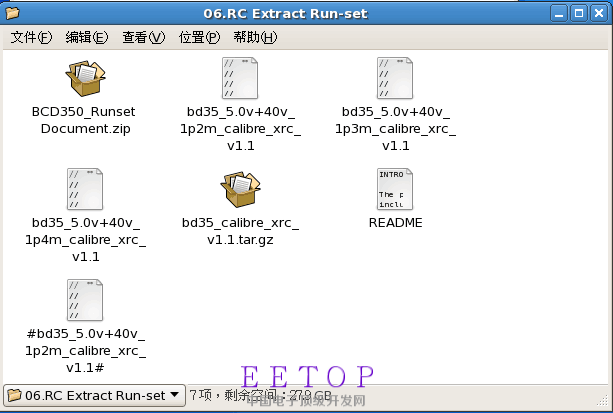

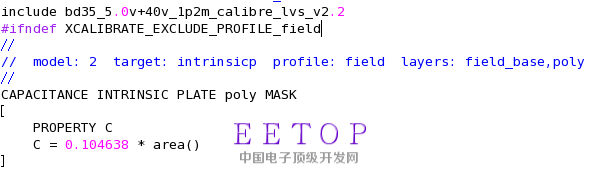

谢谢,第二个问题,我将工艺中的所有XRC文件都试了一遍,都提示这个错误,不应该都有错啊?也试过将这句注释掉,结果又提示CAPACITANCE INTRINSIC PLATE ME1 MASK这一行有错误。

你先将read me文件中的内容看看,怎么说的

erc的问题,你的nwell是不是浮空了?如果是那个是需要接到高电位的

我照着这个改的,没有成功?

这个我知道,确定接到VDD了

你没include是吗?汗……

你check电路不报错吗?

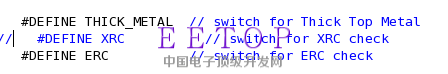

我的XRC文件中没找到include这一句,我加的,我的lvS文件有,lvs通过了,错误只有开始的那个ERC错误。我打开lvs文件将include中的XRC文件换成我PEX要用的,lvs可以运行;后来在开头看到define那一句,不知道为什么注释了,于是将//去掉运行了一遍,结果报错了。

我的XRC文件没找到include这一句,LVS文件中有。