状态机综合后有毛刺如何解决

时间:10-02

整理:3721RD

点击:

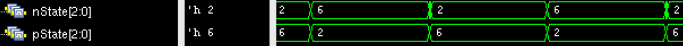

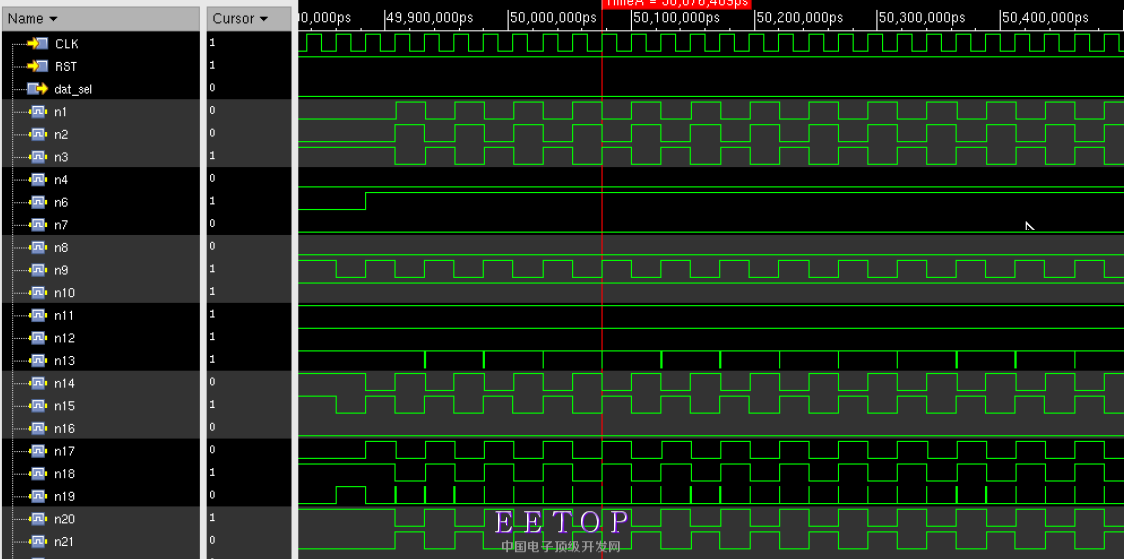

写的状态机使用DC综合后状态跳转时有其他状态存在,有的中间状态和输出有毛刺,这是什么原因,怎么解决?

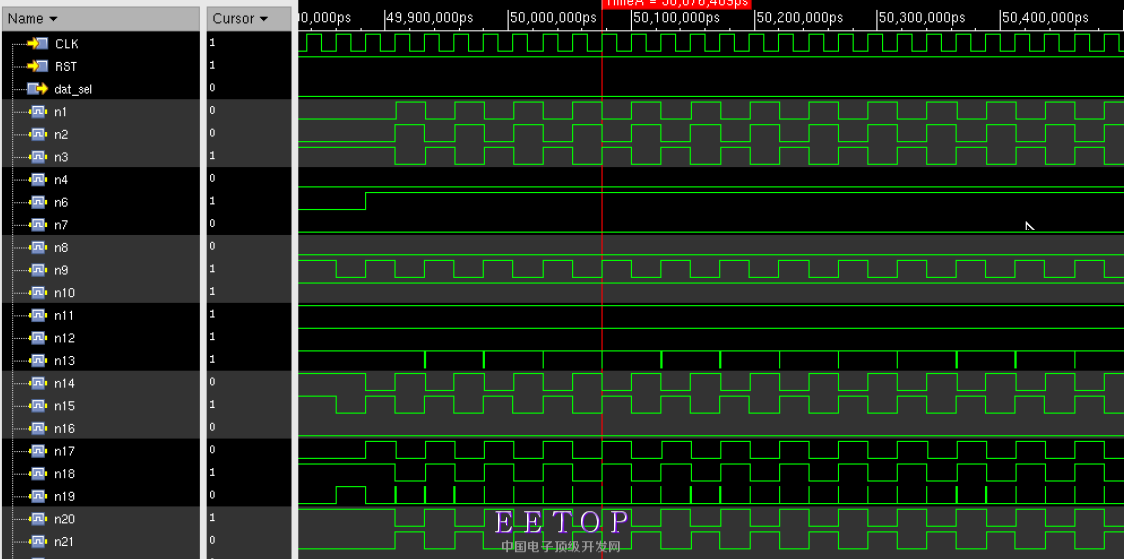

这样看是不是可以,这个状态机里只有一个时钟,怎么处理跨时钟域问题

这样看是不是可以,这个状态机里只有一个时钟,怎么处理跨时钟域问题

组合逻辑有毛刺很正常, 只要跨时钟域处理正确, 而且满足setup和hold, 毛刺是没有问题的。

用独热码

没用过DC综合,但是仿真的时候,状态转移有毛刺,一般都是程序有问题,你好好检查看看,多半是哪里逻辑有问题。感觉和是否是独热码关系不大,反正我个人不用独热码,有的综合器会自动综合成为独热码。

不要误导新人,后端出来网表带SDF 后仿 时, 多bit信号出现毛刺太正常的了。

就算是DFF输出 也不行, 因为多bit DFF的 CK端是可能出现skew的, Q端并不是完全同时改变的。

只要保证setup hold ,是可以保证CLK 是不会 采样到这些毛刺的。

还有跨时钟域要做好,setup hold只能保证 各个clk domain内部的毛刺不会被采样到。

受教。

只做FPGA开发,没用过后仿,我做前仿状态机遇到毛刺一般都是程序的问题。

小编跳过我的回答吧。

5楼正解。

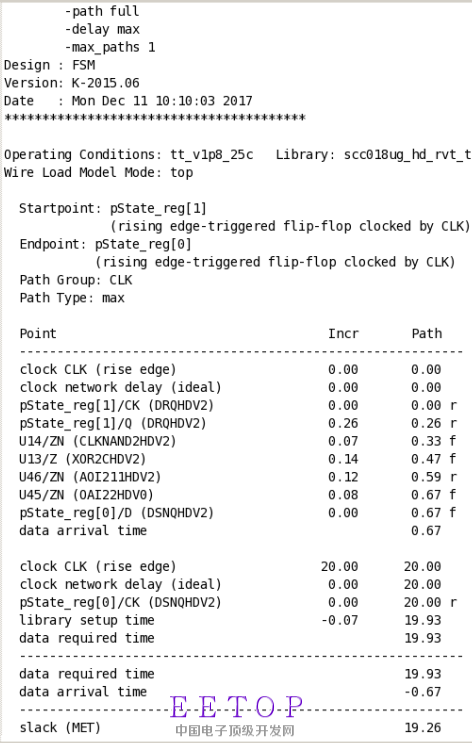

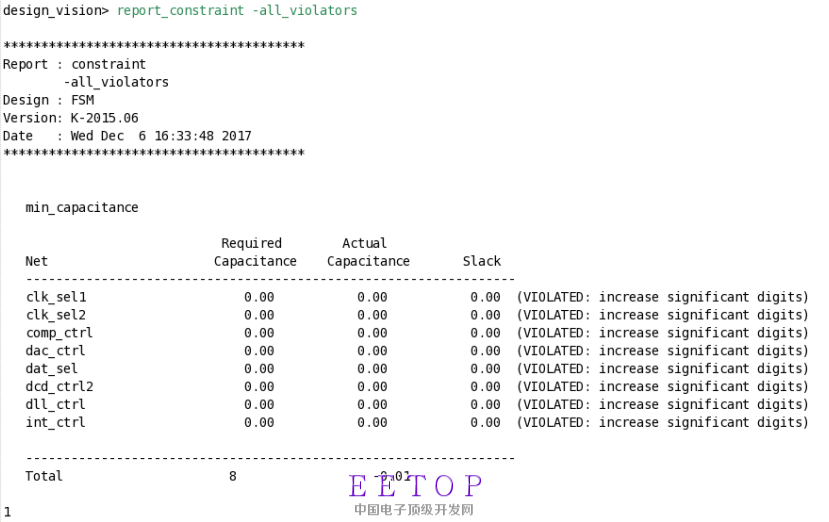

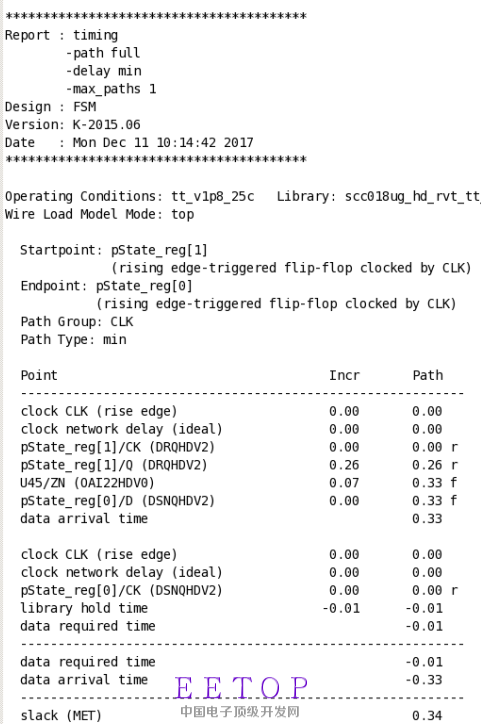

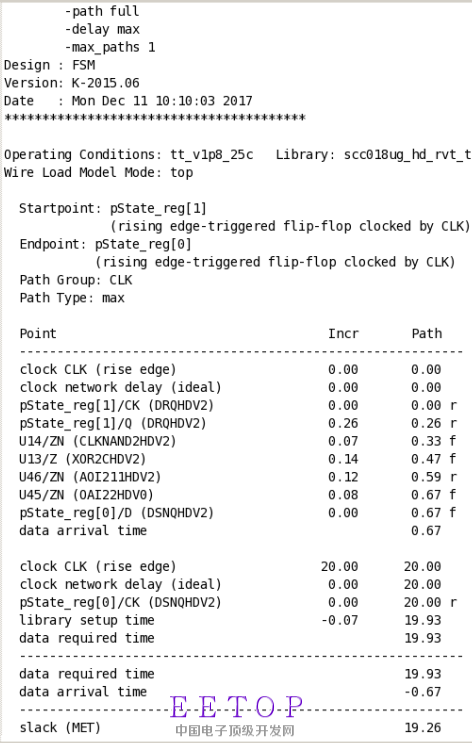

setup和hold是看report_timing里的slack就可以了吗,我用report_constraint有这些问题,这个是什么情况,应该怎么解决?

哪位大神告诉我下setup和hold在DC里具体怎么看

你的报告里有max_delay/setup, min_delay/hold 的内容的,如果没有违例,那就像5楼说的,是不是有些跨时钟域的问题没有解决好?

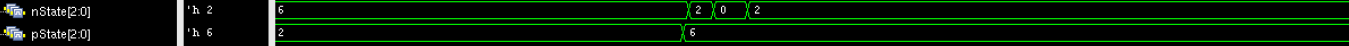

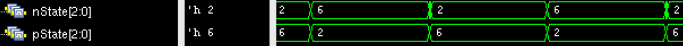

这样看是不是可以,这个状态机里只有一个时钟,怎么处理跨时钟域问题

这样看是不是可以,这个状态机里只有一个时钟,怎么处理跨时钟域问题

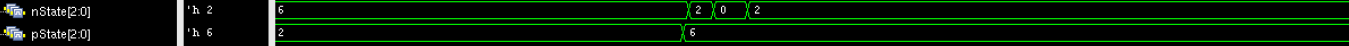

是的,另外,看你这个nstate->pstate跳转不是都正常吗

你RTL仿真都有毛刺?你状态机的所有用到的信号都同步化过么