请问用xilinx ISE 14.7 设计的状态机 一开始的状态怎么定义 仿真出来一开始不是000

时间:10-02

整理:3721RD

点击:

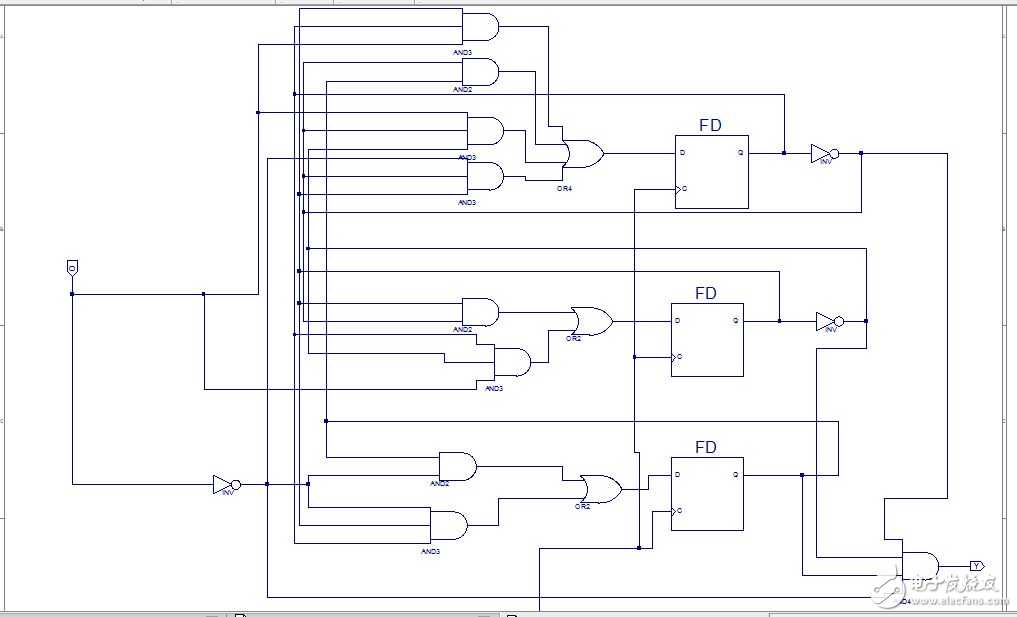

从仿真图看一开始的触发器的状态不是000

你把图和代码贴上来啊

最下面接的是一个寄存器用来接收外部的信号 我这个用来检测00011这个序列的

test bench 的代码

process

begin

clk<='0';

wait for 10 ns;

clk<='1';

wait for 30 ns;

clk<='0';

wait for 20 ns;

clk<='1';

wait for 30 ns;

clk<='0';

wait for 20 ns;

clk<='1';

wait for 30 ns;

clk<='0';

wait for 20 ns;

clk<='1';

wait for 30 ns;

clk<='0';

wait for 20 ns;

clk<='1';

wait for 30 ns;

clk<='0';

wait for 20 ns;

end process;

process

begin

switches<='1';

wait for 50 ns;

switches<='1';

wait for 50 ns;

switches<='0';

wait for 50 ns;

switches<='0';

wait for 50 ns;

switches<='0';

wait for 60 ns;

end process;